- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Other solutions

- STM32H747_DISCO board cannot read Audio Data(MP34D...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H747_DISCO board cannot read Audio Data(MP34DT05TR Mic) based on DFSDM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-05 04:17 AM

Board: STM32H747I-DISO

SDK: STM32Cube_FW_H7_V1.6.0

Pin: PD3(CLK), PC7(DATAIN3)

Problem: Filter->DMA bufer OK. HAL_DFSDM_FilterRegConvCpltCallback and HAL_DFSDM_FilterRegConvHalfCpltCallback function enter normally, but the data is wrong(always the same number).

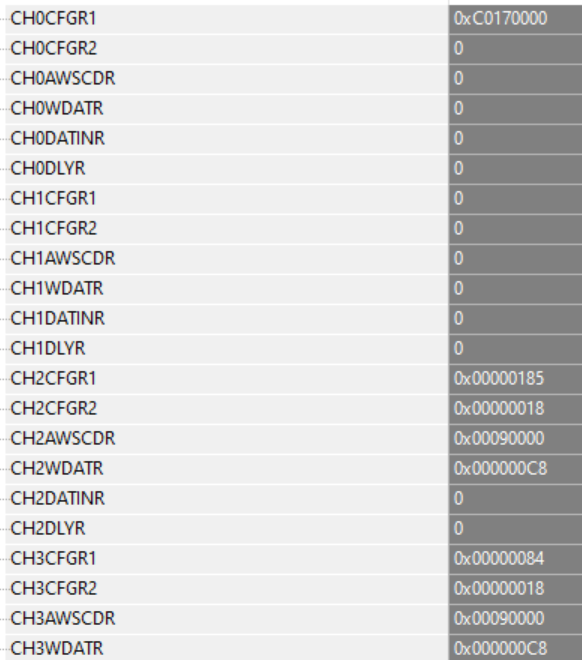

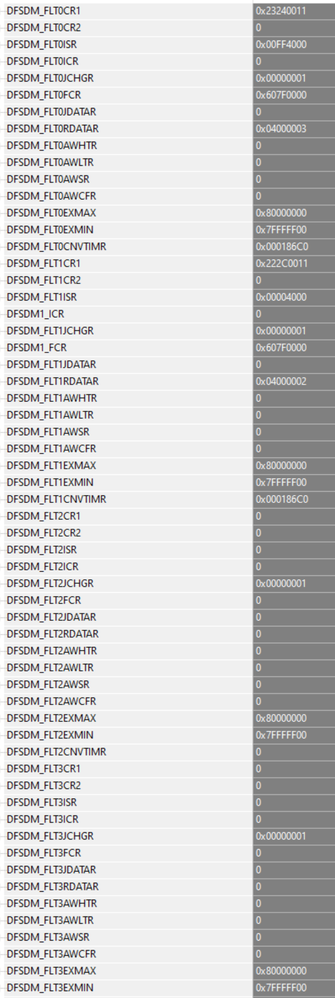

I monitor the DFSDM registers, the RDATAR register no change.

Head Code

/* DFSDM Configuration defines */

#define AUDIO_DFSDMx_RIGHT_CHANNEL DFSDM_CHANNEL_2

#define AUDIO_DFSDMx_LEFT_CHANNEL DFSDM_CHANNEL_3

#define AUDIO_DFSDMx_LEFT_FILTER DFSDM1_Filter0

#define AUDIO_DFSDMx_RIGHT_FILTER DFSDM1_Filter1

#define AUDIO_DFSDMx_CLK_ENABLE() __HAL_RCC_DFSDM1_CLK_ENABLE()

#define AUDIO_DFSDMx_CKOUT_PIN GPIO_PIN_3

#define AUDIO_DFSDMx_CKOUT_DMIC_GPIO_PORT GPIOD

#define AUDIO_DFSDMx_CKOUT_AF GPIO_AF3_DFSDM1

#define AUDIO_DFSDMx_CKOUT_DMIC_GPIO_CLK_ENABLE() __HAL_RCC_GPIOD_CLK_ENABLE()

#define AUDIO_DFSDMx_DMIC_DATIN_PIN GPIO_PIN_7

#define AUDIO_DFSDMx_DMIC_DATIN_GPIO_PORT GPIOC

#define AUDIO_DFSDMx_DMIC_DATIN_AF GPIO_AF4_DFSDM1

#define AUDIO_DFSDMx_DMIC_DATIN_GPIO_CLK_ENABLE() __HAL_RCC_GPIOC_CLK_ENABLE()

/* DFSDM DMA Right and Left channels definitions */

#define AUDIO_DFSDMx_DMAx_CLK_ENABLE() __HAL_RCC_DMA2_CLK_ENABLE()

#define AUDIO_DFSDMx_DMAx_LEFT_REQUEST DMA_REQUEST_DFSDM1_FLT0

#define AUDIO_DFSDMx_DMAx_RIGHT_REQUEST DMA_REQUEST_DFSDM1_FLT1

#define AUDIO_DFSDMx_DMAx_PERIPH_DATA_SIZE DMA_PDATAALIGN_WORD

#define AUDIO_DFSDMx_DMAx_MEM_DATA_SIZE DMA_MDATAALIGN_WORD

#define AUDIO_DFSDMx_DMAx_LEFT_STREAM DMA2_Stream3

#define AUDIO_DFSDMx_DMAx_LEFT_IRQ DMA2_Stream3_IRQn

#define AUDIO_DFSDMx_DMAx_LEFT_IRQHandler DMA2_Stream3_IRQHandler

#define AUDIO_DFSDMx_DMAx_RIGHT_STREAM DMA2_Stream2

#define AUDIO_DFSDMx_DMAx_RIGHT_IRQ DMA2_Stream2_IRQn

#define AUDIO_DFSDMx_DMAx_RIGHT_IRQHandler DMA2_Stream2_IRQHandler

/* Select the interrupt preemption priority and subpriority for the DMA interrupt */

#define AUDIO_IRQ_PREPRIO ((uint32_t)0x0E)

Source Code

static void DFSDM_Init(void)

{

/* Initialize channel 1 (left channel)*/

__HAL_DFSDM_CHANNEL_RESET_HANDLE_STATE(&DfsdmLeftChannelHandle);

DfsdmLeftChannelHandle.Instance = DFSDM1_Channel3;

DfsdmLeftChannelHandle.Init.OutputClock.Activation = ENABLE;

DfsdmLeftChannelHandle.Init.OutputClock.Selection = DFSDM_CHANNEL_OUTPUT_CLOCK_AUDIO;

DfsdmLeftChannelHandle.Init.OutputClock.Divider = 24; /* 49.142MHz/24 = 2.047MHz */

DfsdmLeftChannelHandle.Init.Input.Multiplexer = DFSDM_CHANNEL_EXTERNAL_INPUTS;

DfsdmLeftChannelHandle.Init.Input.DataPacking = DFSDM_CHANNEL_STANDARD_MODE; /* N.U. */

DfsdmLeftChannelHandle.Init.Input.Pins = DFSDM_CHANNEL_SAME_CHANNEL_PINS;

DfsdmLeftChannelHandle.Init.SerialInterface.Type = DFSDM_CHANNEL_SPI_RISING;

DfsdmLeftChannelHandle.Init.SerialInterface.SpiClock = DFSDM_CHANNEL_SPI_CLOCK_INTERNAL;

DfsdmLeftChannelHandle.Init.Awd.FilterOrder = DFSDM_CHANNEL_FASTSINC_ORDER; /* N.U. */

DfsdmLeftChannelHandle.Init.Awd.Oversampling = 10; /* N.U. */

DfsdmLeftChannelHandle.Init.Offset = 0;

DfsdmLeftChannelHandle.Init.RightBitShift = 3;

if (HAL_OK != HAL_DFSDM_ChannelInit(&DfsdmLeftChannelHandle))

{

Error_Handler();

}

/* Initialize channel 0 (right channel)*/

__HAL_DFSDM_CHANNEL_RESET_HANDLE_STATE(&DfsdmRightChannelHandle);

DfsdmRightChannelHandle.Instance = DFSDM1_Channel2;

DfsdmRightChannelHandle.Init.OutputClock.Activation = ENABLE;

DfsdmRightChannelHandle.Init.OutputClock.Selection = DFSDM_CHANNEL_OUTPUT_CLOCK_AUDIO;

DfsdmRightChannelHandle.Init.OutputClock.Divider = 24; /* 49.142MHz/24 = 2.047MHz */

DfsdmRightChannelHandle.Init.Input.Multiplexer = DFSDM_CHANNEL_EXTERNAL_INPUTS;

DfsdmRightChannelHandle.Init.Input.DataPacking = DFSDM_CHANNEL_STANDARD_MODE; /* N.U. */

DfsdmRightChannelHandle.Init.Input.Pins = DFSDM_CHANNEL_FOLLOWING_CHANNEL_PINS;

DfsdmRightChannelHandle.Init.SerialInterface.Type = DFSDM_CHANNEL_SPI_FALLING;

DfsdmRightChannelHandle.Init.SerialInterface.SpiClock = DFSDM_CHANNEL_SPI_CLOCK_INTERNAL;

DfsdmRightChannelHandle.Init.Awd.FilterOrder = DFSDM_CHANNEL_FASTSINC_ORDER; /* N.U. */

DfsdmRightChannelHandle.Init.Awd.Oversampling = 10; /* N.U. */

DfsdmRightChannelHandle.Init.Offset = 0;

DfsdmRightChannelHandle.Init.RightBitShift = 3;

if (HAL_OK != HAL_DFSDM_ChannelInit(&DfsdmRightChannelHandle))

{

Error_Handler();

}

/* Initialize filter 0 (left channel) */

__HAL_DFSDM_FILTER_RESET_HANDLE_STATE(&DfsdmLeftFilterHandle);

DfsdmLeftFilterHandle.Instance = DFSDM1_Filter0;

DfsdmLeftFilterHandle.Init.RegularParam.Trigger = DFSDM_FILTER_SW_TRIGGER;

DfsdmLeftFilterHandle.Init.RegularParam.FastMode = ENABLE;

DfsdmLeftFilterHandle.Init.RegularParam.DmaMode = ENABLE;

DfsdmLeftFilterHandle.Init.InjectedParam.Trigger = DFSDM_FILTER_SW_TRIGGER; /* N.U. */

DfsdmLeftFilterHandle.Init.InjectedParam.ScanMode = ENABLE; /* N.U. */

DfsdmLeftFilterHandle.Init.InjectedParam.DmaMode = DISABLE; /* N.U. */

DfsdmLeftFilterHandle.Init.InjectedParam.ExtTrigger = DFSDM_FILTER_EXT_TRIG_TIM1_TRGO; /* N.U. */

DfsdmLeftFilterHandle.Init.InjectedParam.ExtTriggerEdge = DFSDM_FILTER_EXT_TRIG_RISING_EDGE; /* N.U. */

DfsdmLeftFilterHandle.Init.FilterParam.SincOrder = DFSDM_FILTER_SINC3_ORDER;

DfsdmLeftFilterHandle.Init.FilterParam.Oversampling = 128; /* 49.142MHz/(24*128) = 16KHz */

DfsdmLeftFilterHandle.Init.FilterParam.IntOversampling = 1;

if (HAL_OK != HAL_DFSDM_FilterInit(&DfsdmLeftFilterHandle))

{

Error_Handler();

}

/* Initialize filter 1 (right channel) */

__HAL_DFSDM_FILTER_RESET_HANDLE_STATE(&DfsdmRightFilterHandle);

DfsdmRightFilterHandle.Instance = DFSDM1_Filter1;

DfsdmRightFilterHandle.Init.RegularParam.Trigger = DFSDM_FILTER_SYNC_TRIGGER;

DfsdmRightFilterHandle.Init.RegularParam.FastMode = ENABLE;

DfsdmRightFilterHandle.Init.RegularParam.DmaMode = ENABLE;

DfsdmRightFilterHandle.Init.InjectedParam.Trigger = DFSDM_FILTER_SW_TRIGGER; /* N.U. */

DfsdmRightFilterHandle.Init.InjectedParam.ScanMode = ENABLE; /* N.U. */

DfsdmRightFilterHandle.Init.InjectedParam.DmaMode = DISABLE; /* N.U. */

DfsdmRightFilterHandle.Init.InjectedParam.ExtTrigger = DFSDM_FILTER_EXT_TRIG_TIM1_TRGO; /* N.U. */

DfsdmRightFilterHandle.Init.InjectedParam.ExtTriggerEdge = DFSDM_FILTER_EXT_TRIG_RISING_EDGE; /* N.U. */

DfsdmRightFilterHandle.Init.FilterParam.SincOrder = DFSDM_FILTER_SINC3_ORDER;

DfsdmRightFilterHandle.Init.FilterParam.Oversampling = 128; /* 49.142MHz/(24*128) = 16KHz */

DfsdmRightFilterHandle.Init.FilterParam.IntOversampling = 1;

if (HAL_OK != HAL_DFSDM_FilterInit(&DfsdmRightFilterHandle))

{

Error_Handler();

}

/* Configure regular channel and continuous mode for filter 0 (left channel) */

if (HAL_OK != HAL_DFSDM_FilterConfigRegChannel(&DfsdmLeftFilterHandle, DFSDM_CHANNEL_3, DFSDM_CONTINUOUS_CONV_ON))

{

Error_Handler();

}

/* Configure regular channel and continuous mode for filter 1 (right channel) */

if (HAL_OK != HAL_DFSDM_FilterConfigRegChannel(&DfsdmRightFilterHandle, DFSDM_CHANNEL_2, DFSDM_CONTINUOUS_CONV_ON))

{

Error_Handler();

}

}

- Labels:

-

Audio

-

DFSDM

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-07 01:50 AM

Hello, @zjiaz.1 ,

Do you figure out this issue? I face the same problem and i see around that many others have troubles but there is no answer for now.

I layed my work on stm32h747-eval DFSDM example and i tailored it for my stm32h747i-disco but my left and rightbuf always be filled by same value -16777216 and so when they in SaturaLH the play buf is filled by -32768. So I supposed that it about error configuration on DFSDM init. Is someone can please bring us response?

Thanks,