- STMicroelectronics Community

- Product forums

- Other: hardware

- Questions about MLPF-WB55-02E3 PCB assembly

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Questions about MLPF-WB55-02E3 PCB assembly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-18 11:45 PM

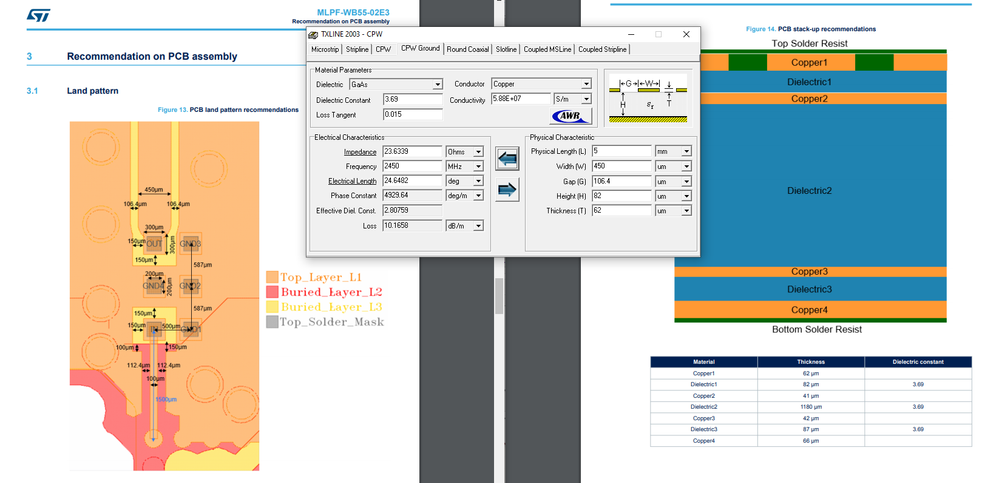

1 On the datasheet MLPF-WB55-02E3 there are recommendation for PCB assembly this chip. The document prescribes to use ground CPW line (on antenna side) with sizes as in the pictures Figure 13. and Figure 14 . The chip MLPF-WB55-02E3 has 50 Ω nominal impedance . I calculated the ground CPW line with sizes as Figure 13, 14 and got a different value (not 50 Ω ). See the attachment: Did I make a mistake?

What impedance should the line have?

Can I make the line according to my PCB stack?

2 On the Figure 13 there is a line from STM32 RF port to input MLPF-WB55-02E3. The line has some sizes. Is the sizes part of the mattching design?

What is this line characteristic?

Can I make the line according to my PCB stack?

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-17 07:39 AM

Hello Dmitriy,

Concerning the line before the filter (RF in I/O) for MLPF-WB55-01E3 , for routing/spacing reason this line cannot be sufficiently wide to be 50 ohms.

Width has been chosen to allow proper routing while length has been minimized to allow proper assembly between STM32WB & MLPF.

- This line (& 2 layers stack up) has been taken into account in MLPF design analysis and must be layouted as close as possible to ensure best performances.

- If this line is modified, performances will not be as described in datasheet.

- in your case line dimension has to be recalculated according to your new 2 layers stackup & material to present same impedance at MLPF input pad : ie characteristic impedance (around 65 ohms) & line length (1.5mm) have to be the same. GND clearance under the MLPF has also to be followed.

so to answer to your questions :

1/ this is correct for MLPF-WB55-01E3 only , due to routing constraint on 2 layers PCB, line between WB55 & MLPF is not 50 ohms

it has of course been taken in to account during MLPF design phase.

2/ 1.5mm length & characteristic impedance @ 65 Ohms.

3/ there will be same routing issue with cap + BPF for the line between WB55 & cap : the line will probably not be 50 ohms for routing constraint on 2 layers PCB & as a consequence line dimensions will have to be changed also according PCB stack up.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-19 05:55 AM

Hello,

concerning your point 1/ for the line between MLPF and antenna, you have to consider reference ground plane in layer 3 and not layer 2 (see fig 13). So H must be set to 1303um which will lead to a 50 ohms impedance.

for point 2, yes the line between STM32 & MLPF is part of the matching, you have to rout a line with same impedance and same length.

GND opening on top layer has also to be carefully routed as close as possible to datasheet recommandation.

best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-19 11:21 PM

Thank you F.Dupont . I can't make exactly PCB stack (Figure 14) so I want to be as close as possible to reference characteristics but with my PCB stack.

1 Does the line ( from STM32 to MLPF-WB55-02E3 ) have 50 ohm impedance and length 1.5mm (Figure 13)?

2 Are there other requirements to this line?

3 Is it ground CPW line with sizes as Figure 13 and H = 82um ?

4 Is the dialectic height under the MLPF-WB55-02E3 important ?

5 Is the copper thickness important ? 62um is too much for me. Can I use lower value with another PCB stack?

6 Could you recommend dielectric material or loss tangent for pcb reference design (Figure 13,14) ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-20 04:30 AM

Hello,

please find below answers to your questions :

1/ Yes this line is 50 ohms impedance , this line is CPWG referenced to layer 2 in order to have a narrow line to allow proper routing up to the STM32WB.

This line must be 1.5mm length.

2 / You have to strictly respect pads size & ground clearance around pads for layer 1.

3/ Yes, this line is referenced to layer 2 to minimize line width for easier routing close to STM32Wb.

4/ Under the MPLF , closest layer is layer 3 ( = no layer 2), this means 1300um diel thickness, so diel height is no critical provided GND plane is sufficiently far. No GND allowed on layer 2 for example.

5/ This will only impact slightly line impedance .

6/ For our ref design Er=3.69 with Df = 0.03

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-20 04:41 AM

Thank you. I'll follow your recommendations.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-06 12:53 AM

Hello, F.Dupont

I have a question about the similar device MLPF-WB55-01E3. My PCB stack has thickness 1 mm, dielectric T180A Er=4.3, Df =0.015, 2 layers, copper 18um. I going to adapt reference design STM32WB55 QFN MLPF-WB55-01E3 for my PCB.

According to reference design there are two line.

Without a doubt the line 2 is 50 Om CPWG.

The characteristics of the first line do not match 50 ohms. This is ~65 Om and 1.5mm length. Impedances of the ICs STM32WB55 QFN and MLPF-WB55-01E3 are unknown, so I have to follow the reference design guidelines. This matching STM32WB55 to MLPF-WB55-01E3 is done on CPWG line 1.

1 Pleas comment my reasoning about line 1 and line 2.

2 Could you give me exact requirements for line 1 ( for custom PCB stack )

3 Another way for RF QFN STM32WB55 port (same as NUCLEO MB1293, MB1355) is capacitor of matching + Band Pass Filter. In a situation where it is not possible to repeat exactly the reference design Is it the best solution for custom PCB stak ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-17 07:39 AM

Hello Dmitriy,

Concerning the line before the filter (RF in I/O) for MLPF-WB55-01E3 , for routing/spacing reason this line cannot be sufficiently wide to be 50 ohms.

Width has been chosen to allow proper routing while length has been minimized to allow proper assembly between STM32WB & MLPF.

- This line (& 2 layers stack up) has been taken into account in MLPF design analysis and must be layouted as close as possible to ensure best performances.

- If this line is modified, performances will not be as described in datasheet.

- in your case line dimension has to be recalculated according to your new 2 layers stackup & material to present same impedance at MLPF input pad : ie characteristic impedance (around 65 ohms) & line length (1.5mm) have to be the same. GND clearance under the MLPF has also to be followed.

so to answer to your questions :

1/ this is correct for MLPF-WB55-01E3 only , due to routing constraint on 2 layers PCB, line between WB55 & MLPF is not 50 ohms

it has of course been taken in to account during MLPF design phase.

2/ 1.5mm length & characteristic impedance @ 65 Ohms.

3/ there will be same routing issue with cap + BPF for the line between WB55 & cap : the line will probably not be 50 ohms for routing constraint on 2 layers PCB & as a consequence line dimensions will have to be changed also according PCB stack up.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-29 11:17 PM

Thank you, F.Dupont

- Need Help for PCB Design Problem Solution in STM32 MCUs Boards and hardware tools

- Question about LSM303AGR_ACC_SENSITIVITY_2G definition in lsm303agr.h in MEMS (sensors)

- ST25R3911B EMI test failed in ST25 NFC/RFID tags and readers

- Really *** question - Running software without debugger in STM32 MCUs products

- I can't blink my leds in H755ZI Nucleo board in STM32 MCUs products