- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- PWM input falling edge capture behavior

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PWM input falling edge capture behavior

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 07:35 AM

Hi,

I'm following RM0390 reference manual's PWM input mode example for calculating frequency and duty cycle for incoming PWM signal. Basically I'm using TIM1's CC1 for capturing rising edges and CC2 for capturing falling edges. The question is that is it normal for CC2 to be triggered twice in a period? It seems that in my case CC2 is also sensitive for rising edges. Is that due to timer reset?

If the behavior described above is normal, do I just discard the CC2 value when CC1 gets triggered? Also if I want to use input capture prescaling do I configure IC2PSC to be twice as many events as IC1PSC?

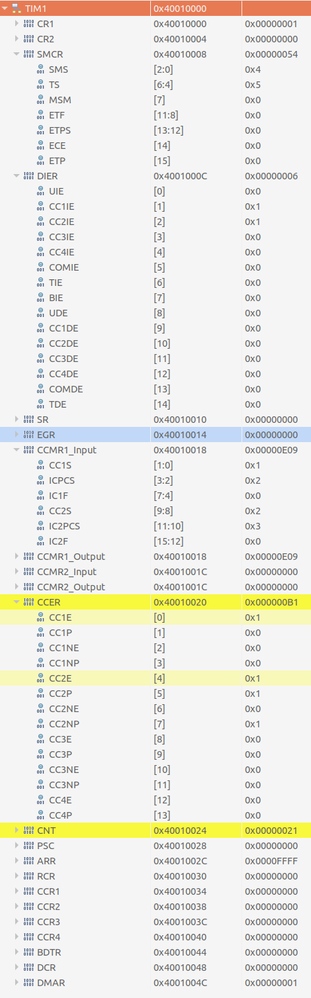

Here's my TIM1 register just after CC1 and CC2 have been enabled.

Solved! Go to Solution.

- Labels:

-

Documentation

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 03:51 PM

You've set both CC2P and CC2NP in CCER, that's both edges sensitivity.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 03:51 PM

You've set both CC2P and CC2NP in CCER, that's both edges sensitivity.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-20 09:59 AM

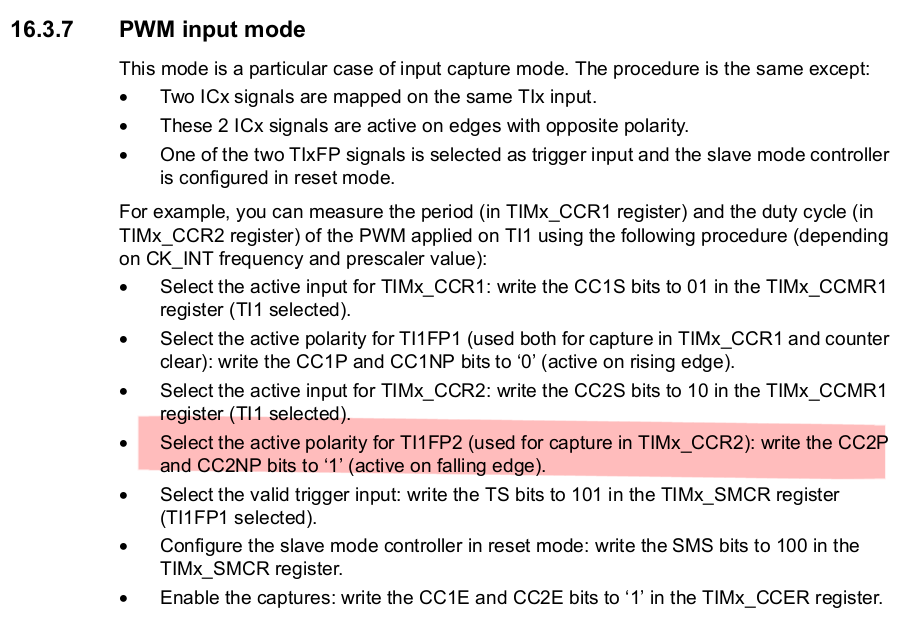

Thanks! Looks like disabling CC2NP bit solves my problem. I re-visited RM0390's PWM input mode example and it states that both CC2P and CC2NP should be enabled. Maybe I have misunderstood something.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-20 10:58 AM

Eetu,

Humm, that's a bug in the manual. Thanks for letting us know.

I randomly selected RM0090 rev.18 and it's incorrect in 2 out of the 3 incarnations of the PWM input mode subchapter (it's correct in the TIM2-TIM5 chapter). I guess it will be similar for RM0390.

@Imen DAHMEN this probably goes across many STM32 TIM chapters, can somebody please have a look at it?

Thanks,

JW

#sloppy_manual_revisioning

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-28 08:11 AM

Hi @Community member ,

I'll take care of this. It will be changed in the source file and will be visible when new user manuals will be published.

Best regards,

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-28 10:03 AM

Thanks, Vincent.

Jan

@Vincent Onde

- G431RBT6 - Interfacing timer and compare output timer have rather fluctuation timings in STM32 MCUs products

- STM32H7 TTCAN Time Reference Messages with External Loopback Mode? in STM32 MCUs products

- Delay of interfacing timer is rather inconsistent in STM32 MCUs products

- Timer input capture interrupt fires over and over - Not a late flag reset issue (probably) in STM32 MCUs products

- Pullup does not work when setting up for timer input capture in STM32 MCUs products