- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- SPI slave mode configuration requires user definit...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI slave mode configuration requires user definition of clk rate

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-12 12:21 PM

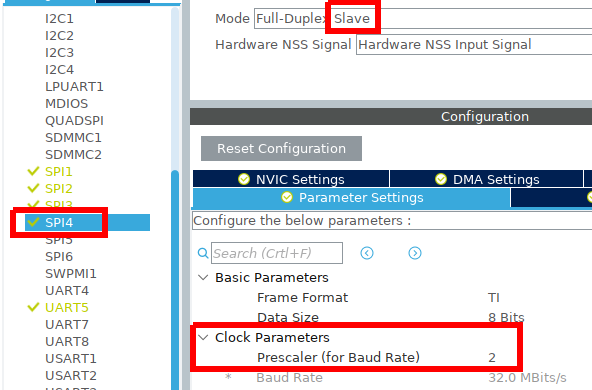

in stm32cubeMX configuration of SPI in slave mode, it asks for user parameter input for clk prescaler, which then derives the clk rate. My understanding for SPI operated in SLAVE mode is that the master end, instead of the slave end, generates the clock.

Is there a way to better understand the purpose of this setting, highlighted in the screenshot? Thanks.

Solved! Go to Solution.

- Labels:

-

SPI

-

STM32Cube MCU Packages

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-16 11:19 AM

> For a slave, its maximum functional baud rate depends on its clock (hence its prescaler).

I don't think this is the case. In slave mode, maximum input frequency is fPCLK/2, regardless of baudrate setting.

However, specifically in TI mode (and that appears to be selected in the OP), the baudrate setting determines the timing for threestating MISO, see the SPI chapter, SPI TI protocol in slave mode subchapter, in RM

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-12 01:12 PM

Cannot confirm your observation for STMCubeMX 5.4.0 and the few chips I have tried.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-12 01:16 PM

Thanks for looking into this problem. Here is my environment:

STM32H742ZGTx Device from STM32H7 series

Linux version CubeMX

- Version: 1.1.0

- Build: 4551_20191014-1140 (UTC)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-12 03:57 PM

For a slave, its maximum functional baud rate depends on its clock (hence its prescaler).

Typically if the SPI is programmed as master 10 MHz SCK frequency, if you turn it as slave with same prescaler settings, the slave will work with max 5MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-16 11:19 AM

> For a slave, its maximum functional baud rate depends on its clock (hence its prescaler).

I don't think this is the case. In slave mode, maximum input frequency is fPCLK/2, regardless of baudrate setting.

However, specifically in TI mode (and that appears to be selected in the OP), the baudrate setting determines the timing for threestating MISO, see the SPI chapter, SPI TI protocol in slave mode subchapter, in RM

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-16 12:39 PM

Thanks to everyone here to help me understand this issue from different angles 🙂

In the RM, SPI specific modes and control -- TI mode, here is the rationale to set the "Baud rate", now I understand it is in fact a signal integrity timing choice.

"In slave mode, the clock generator is used to define time when the slave output at MISO pin becomes to HiZ when the current transaction finishes. The master baud setting is applied and any baud rate can be used to determine this moment with optimal flexibility."

- Is VREF+ pin required to be connected if VREFBUF is configured as an internal reference on STM32G4? in STM32 MCUs products

- Readout external ADC by SPI doesn't work correctly in STM32CubeIDE (MCUs)

- Build issue as variable defined once more, however it is only defined once in STM32CubeIDE (MCUs)

- configuring isr with cmsis rtos v2, debug trace lands at configASSERT funtion call in STM32 MCUs Embedded software

- Using SRAM2a for standby mode on STM32WB15 in STM32 MCUs Wireless