- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- ETR prescaler bandwidth on STM32F401RC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ETR prescaler bandwidth on STM32F401RC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-12 05:53 AM

Hello,

I tried to prescale the TIM2_ETR signal on STM32F401RC, to increase the bandwith.

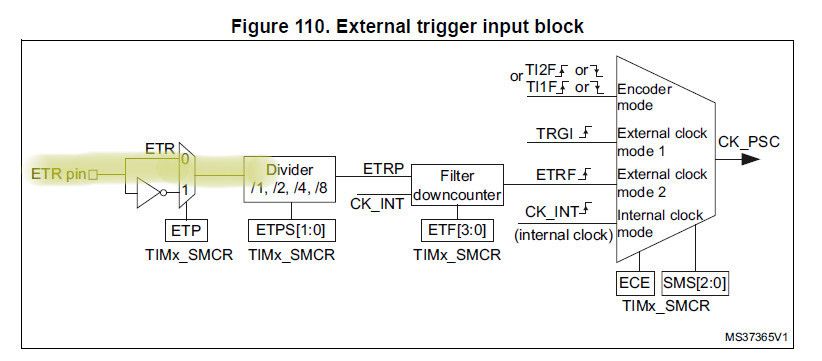

In theory the ETR signal max frequency is 1/4 Fclock = 21 MHz, but it can be increased thanks to the prescaler. The RM0368 manual (STM32F401 reference manual) writes on page P356 " External trigger signal ETRP frequency must be at most 1/4 of CK_INT frequency. A prescaler can be enabled to reduce ETRP frequency. It is useful when inputting fast external clocks."

Indeed I could measure up to 21 MHz = 84MHz/4. Then I prescaled the ETR signal using "4" and "8" predefined prescaling values with this result:

- the ETR signal is prescaled. The counter counts 1/4 or 1/8 of the edges.

- but the maximum frequency is still 21 MHz. Anything above gives wrong (folded?) results.

I tried changing the GPIO speed without any change. Is there anything else to set to increase the bandwidth?

The code I use is:

// Code for Counting TIM2_ETR rising edges

// Setup PA0 alternate function

GPIOA->MODER |= (1<<1); //set bit 1

GPIOA->MODER &= ~(1<<0); //clear bit 0 //MODER0 = 10: alternate function mode

GPIOA->OTYPER &= ~(1<<0); // port output type register: push pull (see table 24 in STM32F401 reference manual

GPIOA->PUPDR &= ~(0b11U<<0);

GPIOA->PUPDR |= (1<<0); // 01 at pin 0: pull up

GPIOA->AFR[0] |= (1<<0);

GPIOA->AFR[0] &= ~(0b111U<<1); // Alternate function AF1: TIM2

// Initializing TIM2

RCC->APB1ENR |= RCC_APB1ENR_TIM2EN; // RCC APB2 clock enable

TIM2->CR1 = 0; // Stops timer

TIM2->CR2 = 0;

// ETR prescaler

(TIMER2->regs).gen->SMCR |= TIMER_SMCR_ETPS_DIV4;

TIM2->SMCR = TIM_SMCR_ECE | (0x3UL << 0); // External clock enable, encoder mode 3: this setting for free running counter

TIM2->CCMR1 = 3; // TIMER_IC_INPUT_TRC ; // Works when TIMx_SMCR.TS is set. Here it is ITR0 master /slave signal from TIM1 to TIM2 signal

// Starts timer

TIM2->CR1 = TIM_CR1_CEN;- Labels:

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-12 06:01 AM

What frequency are you trying to apply?

There is a clock domain resynchronizer on the input, it will have nyquist properties.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-12 06:22 AM

Here the input is ETR. If I am correct, there is no sync mechanism before the ETR prescaler. I tried to measure the highest frequency possible and increased in steps of 1 MHz. It works @ 20MHz, 21 MHz, then the measurement is false even when setting an ETR prescaler value.

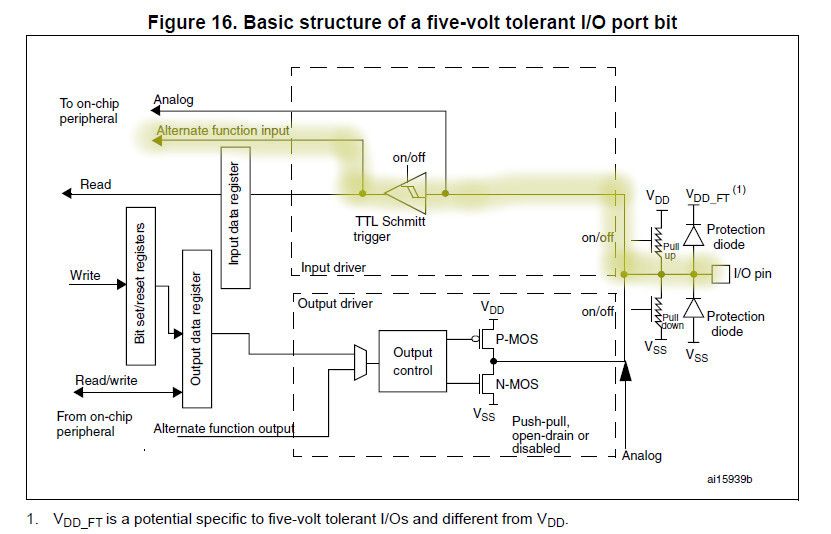

But, do you mean that all inputs have a resync mechanism? I am not talking about data acqusition. There is a signal to alternate function input after the schmidt trigger. I don't see any sync on the "Basic structure of a five-volt tolerant I/O port bit" Also I changed the speed settings of the IO just for a check, and it did not change the max frequency measurable (21 MHz).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-12 06:31 AM

>>If I am correct, there is no sync mechanism before the ETR prescaler.

That might be your expectation, it is not mine.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-12 06:46 AM

Here are the two input block schematics. I don't see where they are synced anywhere before "ETPS"