- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs Embedded software

- Ethernet clock + reset signals don't do anything

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Ethernet clock + reset signals don't do anything

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-12 11:34 AM

Hello ST community

I am having trouble configuring the Ethernet PHY on my custom board using the stm32mp153aac. The MPU is supposed to generate a 50 MHz reference clock for the transceiver, but when I measure the pin with the oscilloscope I get nothing. The reset pin also seems to be configured as input and never changes.

The ethernet transceiver is connected according to "Figure 46. 10/100M Ethernet PHY connection with REFCLK from RCC example" (external ETH_CLK 50 MHz reference, RMII mode, 100 Mbit).

I followed the ST wiki on ethernet device tree configuration and also found this forum thread.

https://wiki.st.com/stm32mpu/wiki/Ethernet_device_tree_configuration

Here is my top-level device tree source file:

And here is stm32mp153a-raichu-cubemx-mx-u-boot.dtsi:

The relevant sections are:

ðernet0{

pinctrl-names = "default", "sleep";

pinctrl-0 = <ð1_pins_mx>;

pinctrl-1 = <ð1_sleep_pins_mx>;

status = "okay";

/* USER CODE BEGIN ethernet0 */

mac-address = [df921222a51c];

phy-mode = "rmii";

max-speed = <100>;

phy-handle = <&phy0>;

st,eth_ref_clk_sel;

snps,reset-active-low;

snps,reset-delays-us = <0>, <10000>, <1000000>;

snps,reset-gpio = <&gpiob 0 GPIO_ACTIVE_HIGH>;

/*enable-gpios = <&gpiob 0 GPIO_ACTIVE_HIGH>;*/

clock-names = "stmmaceth",

"mac-clk-tx",

"mac-clk-rx",

"eth-ck",

"syscfg-clk",

"ethstp";

clocks = <&rcc ETHMAC>,

<&rcc ETHTX>,

<&rcc ETHRX>,

<&rcc ETHCK_K>,

<&rcc SYSCFG>,

<&rcc ETHSTP>;

mdio0 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "snps,dwmac-mdio";

phy0: ethernet-phy@3 {

reg = <3>;

};

};

/* USER CODE END ethernet0 */

};eth1_pins_mx: eth1_mx-0 {

pins1 {

pinmux = <STM32_PINMUX('A', 1, AF11)>, /* ETH1_REF_CLK */

<STM32_PINMUX('C', 1, AF11)>, /* ETH1_MDC */

<STM32_PINMUX('G', 8, AF2)>, /* ETH1_CLK */

<STM32_PINMUX('G', 13, AF11)>, /* ETH1_TXD0 */

<STM32_PINMUX('G', 14, AF11)>; /* ETH1_TXD1 */

bias-disable;

drive-push-pull;

slew-rate = <1>;

};

pins2 {

pinmux = <STM32_PINMUX('A', 2, AF11)>; /* ETH1_MDIO */

bias-disable;

drive-push-pull;

slew-rate = <0>;

};

pins3 {

pinmux = <STM32_PINMUX('A', 7, AF11)>, /* ETH1_CRS_DV */

<STM32_PINMUX('C', 4, AF11)>, /* ETH1_RXD0 */

<STM32_PINMUX('C', 5, AF11)>, /* ETH1_RXD1 */

<STM32_PINMUX('G', 12, AF11)>; /* ETH1_PHY_INTN */

bias-disable;

};

pins4 {

pinmux = <STM32_PINMUX('B', 11, AF11)>; /* ETH1_TX_EN */

};

};pll4:st,pll@3 {

cfg = < 3 99 11 7 7 PQR(1,0,0) >;

u-boot,dm-pre-reloc;

};I would appreciate any insight as to why the reset pin doesn't work and why the 50 MHz ETH_CLK isn't output.

Thanks!

- Labels:

-

OpenSTLinux

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-06 10:20 AM

Hello

please see the OLS request 94533.

Regards,

Emmanuel Combette

STMicroelectronics / T.O.M.A.S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-09 08:12 AM

Hi @Emmanuel COMBETTE DE RYMON

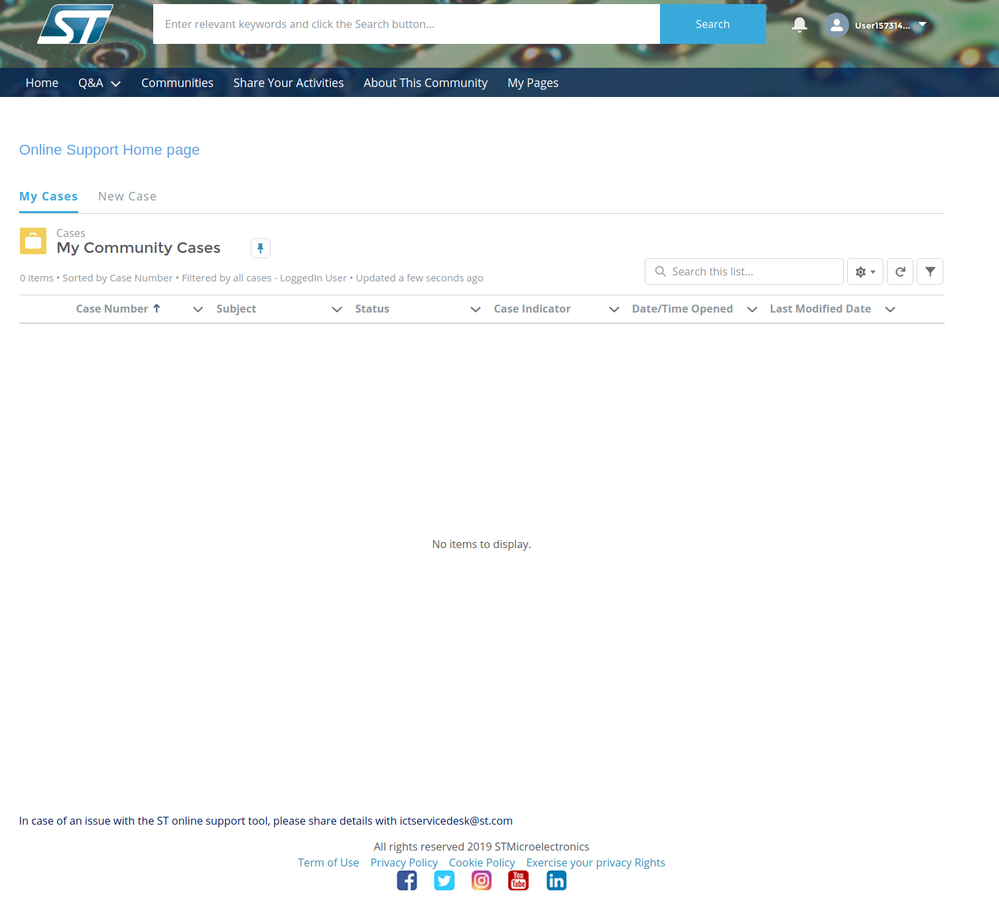

I am trying to find my OLS case 94533 but it's not showing up in my list. This is all I see when I go to my.st.com/ols:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-13 09:12 AM

Hi

1/Regarding the clock "I am having trouble configuring the Ethernet PHY on my custom board using the stm32mp153aac.

The MPU is supposed to generate a 50 MHz reference clock for the transceiver, but when I measure the pin with the oscilloscope I get nothing. The reset pin also seems to be configured as input and never changes. The ethernet transceiver is connected according to "Figure 46. 10/100M Ethernet PHY connection with REFCLK from RCC example" (external ETH_CLK 50 MHz reference, RMII mode, 100 Mbit)."

Looking at the schematics sent by Christopher your schematic are saying that you are in the case of Figure 45 in AN5031 with the crystal option :

R22 not installed and crystal resonator is installed, R28 is mounted (in red)

this means that:

-The 50Mhz ETH_CLK input from transceiver is not expected by the STM32MP1.

-The MP1 expects to get the 50 MHz ref clock from REF_CLK pin from transceiver side

-We do not expect a clock out of MP1 ETH_CLK pin.

In this case st,eth_ref_clk_sel should be removed from your device tree.

can you try and let me know ?

2/Regarding the REST,according to the PHY transceiver DS.

The PHY RST pin ,connected to GPIO B0, is active low. it expects to be high most of the time and when reset is requested

the reset the pin goes from Low during a short period (reset asserted) and then to high state (reset de-asserted).

Looking at the code of the stmmac sdio driver (drivers/net/ethernet/stmicro/stmmac/stmmac_mdio.c)

this should be fine

snps,reset-delays-us = <0>, <10000>, <1000000>;

snps,reset-gpio = <&gpiob 0 GPIO_ACTIVE_LOW>;

snps,reset-active-low = <1>;

Warm Regards,

Emmanuel Combette

T.O.M.A.S

- STM32MP1: USB OTG: wake up when USB plugged/unplugged in STM32 MPUs products

- LibGPIO Chip/Line mapping to physical CN8 pins in STM32 MPUs products

- STM32MP1 ETH_PHY_INTN in STM32 MPUs products

- Linux 6.1 does not get ethaddr from u-boot env in STM32 MPUs products

- RMGII Routing guidelines for STM32MP151XXX in STM32 MPUs products