- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Has a problem when using STM32F405 spi + dma as a...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Has a problem when using STM32F405 spi + dma as a slave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-25 11:37 PM

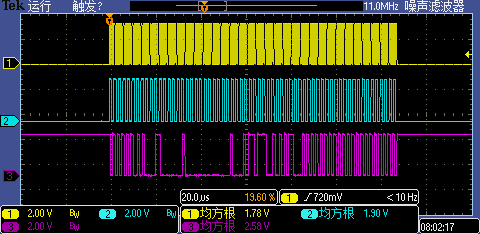

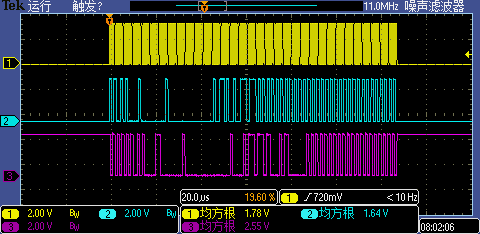

Use STM32F405's SPI + DMA as a slave, circular mode, DMA 16bytes interrupt, but every time send 16bytes to master, the first byte is always the byte that last frame's last byte , it looks like spi tx register is not clear, always contain the last byte, so my question is how can i avoid this problem?

- Labels:

-

DMA

-

SPI

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 02:42 AM

The slave sends the same byte two times, once at the end of the previous frame and then again at the beginning of the next frame?

Is there some NSS activity from the master?

Post relevant oscilloscope/logic analyzer screenshots.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 03:40 AM

Reset always the SPI after communication ended, for debug.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 06:58 PM

hi,

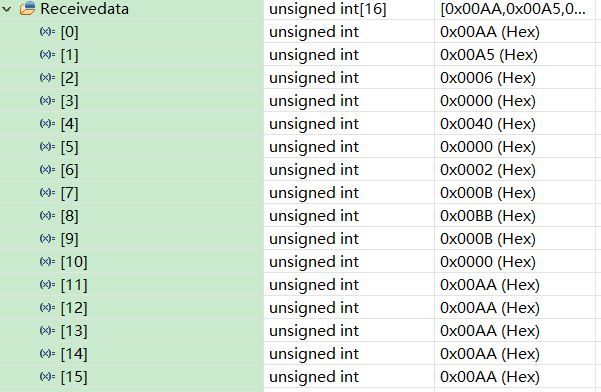

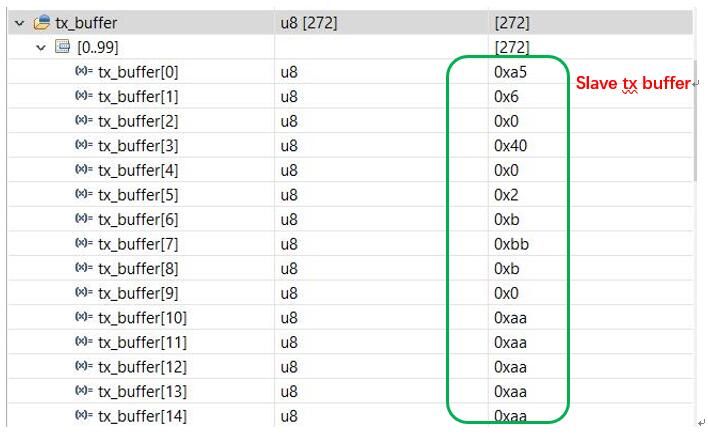

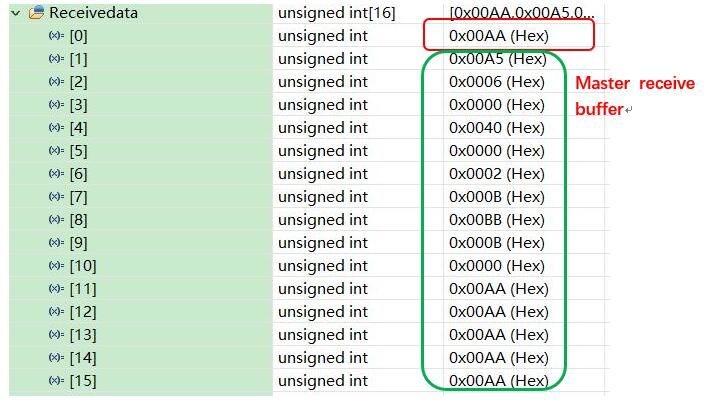

No NSS activity from master, just three lines, slave send(hex) A5 06 00 40 00 02 0B BB 0B 00 AA AA AA AA AA AA

but master receive (hex) AA A5 06 00 40 00 02 0B BB 0B 00 AA AA AA AA AA everytime, looks like last AA is always in the spi tx register

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 06:59 PM

hello. what function do i use to reset spi communication?

is this the only way?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 10:23 PM

it should be somewhere in RCC or SYS of reference manual. Sorry, don't have time to browse and pinpoint anymore.

The reset will work across all the SPI generations. Other milder fix won't cross generation IP boundaries (especially the one with 32 bit FIFOs)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 10:51 PM

Thanks, i find this function “__HAL_RCC_SPI1_FORCE_RESET()�?,but if i reset spi by using this, do i have to initialize SPI again ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 11:11 PM

Then this is classical mis-synchronization, the master starts somewhat sooner than the slave, so when master starts clocking slave has not prepared data yet, and master sees some bogus data as the very first byte (maybe 0xFF or 0x00, depends on circumstances).

You need to concentrate on the very beginning of the communication just after reset, probably you'll need to signal somehow from slave to master that slave is ready.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-26 11:35 PM

hi JW

actually, i'm sure slave is ready, because when i see the slave spi tx buffer is already loaded with new data then i start next master transmit manually, but the first byte is still 0xAA when master received, i think 0xAA is the last byte that last frame send , it stays in spi tx register, am i right?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-27 01:52 AM

The DMA stores a byte into the SPI Tx holding register whenever it sees it is empty.

So yes, 0xAA is from the end of the previous transaction.

I meant, if you control the very first transaction after reset, you shouldn't run into this kind of mis-synchronization. If the slave has always exactly16 bytes to transfer, and the master will always receive 16 bytes, ever since from the reset, you can't see the pattern you see.

JW

- i2c in STM32CubeIDE (MCUs)

- STM32F030C6T6 SPI DMA alignment problems in STM32 MCUs Embedded software

- G431RBT6 - Interfacing timer and compare output timer have rather fluctuation timings in STM32 MCUs products

- UART not listening for transmission after function executing in STM32 MCUs products

- I2C in STM32CubeIDE (MCUs)