- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Increase EEPROM Erase/Write cycles capability for ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Increase EEPROM Erase/Write cycles capability for STM32L0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-16 01:54 AM

Hello all,

I am using the STM32L071KB in a project, and I have to write a 32 bit word in internal EEPROM each minute;

So is it worth changing the address of this 32 bit word after 100 000 cycles, in order to increase number of Erase/Write cycles ?

If the MCU erases the whole EEPROM at each Erase/Write cycle, that would not be worth. But I don't see this information in the user manual.

Thanks !

Solved! Go to Solution.

- Labels:

-

EEPROM devices

-

STM32L0 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-16 01:28 PM

The EEPROM erase granularity is word, i.e. 32 bits, in the 'L0 - and I believe did found that information in the RM. At least that's how it appears to the user; indeed, the true erase mechanism may involve internally buffering a larger page, erasing it, and writing it back. And mcu manufacturers - not only ST - for some strange reason very often don't advertise clearly the true mechanism even if it's a favourable one, i.e. if there's no such internal larger page.

If you are willing to spend one chip for the case, you can try it yourself; IMO a self-concocted test is definitive enough in this case. Of course, you can always try to ask ST - not here, this forum is visited by ST only casually - but through the web support form, or through your FAE, if you have one at hand.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-16 03:16 AM

The word-wise erase/write capability and higher durability are normally features of EEPROM justifying its higher price in relation to FLASH.

I don't know the L071, but don't expect it to be different. I would double-check the datasheet.

First, the 100.000 number is usually guaranteed for the max. temperature, and roughly double for each 10C you go colder.

Second, consider a change in strategy. Like keeping data in RAM, and save only on power-off (or similar event).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-16 06:13 AM

Dear Ozone,

Thanks for your answer; in fact the op temperature can be relatively high, and we don't know when the MCU is powered OFF (so keeping data in RAM will not solve the problem).

That's why we would like to change the data address after 100 000 E/R cycles, but we don't know if it will solve the problem . ST doesn't decribe enough the EEPROM Erase/Write process.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-16 06:38 AM

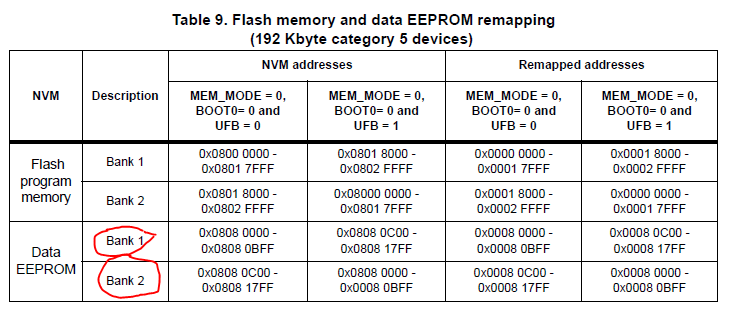

Starting a project involving EEPROM or FLASH erase/program begins with carefully reading the manuals:

The datasheet (DocID027101 Rev 3) says:

Flash program and data EEPROM are divided into two banks. This allows writing in one bank while running code or reading data from the other bank.

The reference manual (DocID025942 Rev 😎 says:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-16 08:15 AM

You're either going to need to use an external EEPROM that meets your requirements, or create a more complex driver that manages cycle counts, and does wear-leveling. One of the most simple strategies being to journal writes across the memory, and then recover the last written values, rather than grinding data on a single spot.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-16 01:28 PM

The EEPROM erase granularity is word, i.e. 32 bits, in the 'L0 - and I believe did found that information in the RM. At least that's how it appears to the user; indeed, the true erase mechanism may involve internally buffering a larger page, erasing it, and writing it back. And mcu manufacturers - not only ST - for some strange reason very often don't advertise clearly the true mechanism even if it's a favourable one, i.e. if there's no such internal larger page.

If you are willing to spend one chip for the case, you can try it yourself; IMO a self-concocted test is definitive enough in this case. Of course, you can always try to ask ST - not here, this forum is visited by ST only casually - but through the web support form, or through your FAE, if you have one at hand.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-16 11:23 PM

Hi JW,

Yes, this si exactly the problem; we don't know if erasing a 32 bit word erases in fact just the 32 bit word, or a whole page (buffered in RAM and writed back to Flash).

I have asked 2 days agao to ST support, but no answer yet...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-18 07:55 AM

Hi,

ST support just answered us :

the EEPROM in STM32L071 is organized by words (4 bytes) and erase operation erases only selected word. Thus 100k cycles is valid per each word separately.

And they confirm that we can write several millions of times the same data in EEPROM, if we increment the address every 100k cycles.

So very good news !

Olivier

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-18 11:19 AM

Thanks for sharing the information.

ST, might consider adding this information clearly into the L0 DS/RM, or maybe better yet, writing an appnote (in black and white please). The EEPROM ought to be one of the selling points of the 'L0 line, but IMO the available materials fail to emphasize this, in clear and complete engineering terms, and this thread witnesses that too.

JW

@Imen DAHMEN , @Amel NASRI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-27 02:40 AM

Hello @Community member ,

Good point. I raised the request for change in the coming reference manuals.

Best Regards,

Imen

Thanks

Imen

- Timer callback issue? in STM32 MCUs products

- Question about ST MCSDK 6-Step Algorithm Capabilities in STM32 MCUs Motor control

- STM32F407 USB Device HS mode interrupt transmission jitter in STM32 MCUs products

- Why PSRAM is slower than SRAM and how can one increase the speed of PSRAM in STM32L4R8I. in STM32 MCUs products

- OV5640 JPEG Compression Issue When Storing Images on SD Card with STM32 in STM32 MCUs Embedded software