- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- H743 ADC cannot be set to synchronous clock mode w...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

H743 ADC cannot be set to synchronous clock mode when AHB clock is 100MHz. the constraint seem to be wrong?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-29 10:10 PM

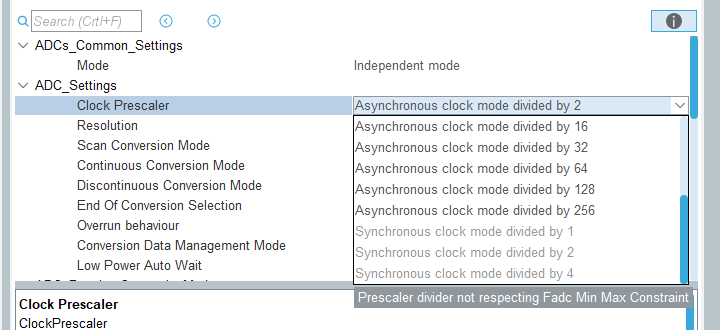

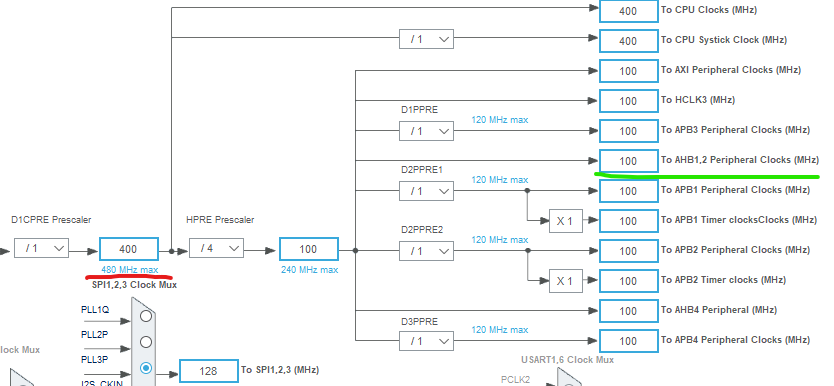

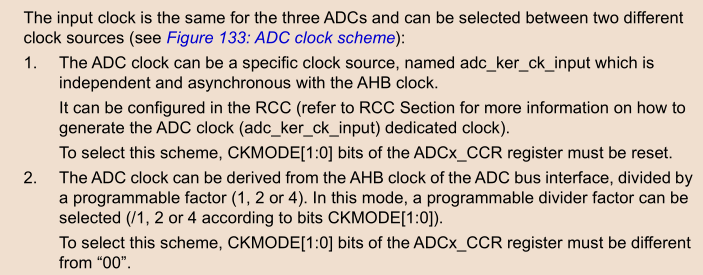

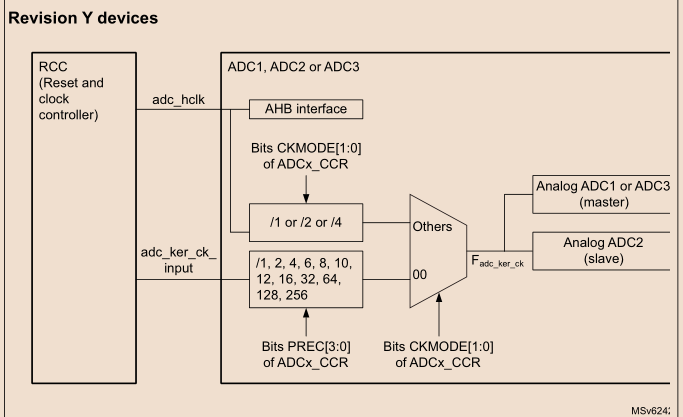

According to my understanding of the manual, setting ADC1 to synchronous clock mode requires selecting the clock source as AHB. The constraint should be the AHB1 frequency (green mark). However, CubeMX use D1CPRE clock (red mark) as a constraint. Synchronous clock mode optional only available when the D1CPRE frequency is low enough(In that case CPU clock is too low).

Is this a CubeMX bug, or I have misunderstood the manual?

- Labels:

-

ADC

-

Bug-report

-

RCC

-

STM32CubeMX

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-13 12:57 AM

Hello @Zack

could you please share ypur ioc file ?

thanks,

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-13 03:38 AM

I have tested this by myself using H743BITx,

Well, the synchronous/asyn clock mode divided by x should respect the Fadc min, max constraint :

the Fadc min, max constraint is :

according to an RCC Parameter: Power Regulator voltage Scale 1 or 2 or 3 we define a max and min Fadc constraint.

the asynchronous/synchronous clock mode divided by x can be selected only if :

Fadc min < ADCClockSynch/x < Fadc max & Fadc min < ADCClockASynch/x < Fadc max.

for example in our case we use STM32H7

-the ADCClockSynch =140 MHz

- the power Regulator Voltage Scale is set to power Regulator Voltage Scale 1 => that give us a Fadc min = 140 KHz and Fadc max = 36 MHz

we take the example of asynchronous clock mode divided by 4

1/

140Mhz / 4 = 35 MHz Fadc min= 140 KHz < 35Mhz< fadc max = 36 Mhz then the asynchronous clock mode divided by 4 can be used .

2/

280 MHz /4 = 70 MHz > Fadc max =36 MHz then asynchronous clock mode divided by 4 not allowed.

that why the not allowed divider are grayed in Mx.

Best Regards,

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-17 11:50 PM