- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- adc trigger on timer is at half frequency

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

adc trigger on timer is at half frequency

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-04 02:05 PM

Hi all,

ADC triggering appears to be at half the frequency of the timer, (ie occurs every 2 update events), is this expected ?

This is with a STM32F334 progammed using HAL and with code generated by CubeMX.

I am reading 14 ADC channels using DMA (2x7 in simultaneous sampling), with interrupt at end of all conversions (HAL_ADC_ConvCpltCallback), values are found correct in the DMA buffer.

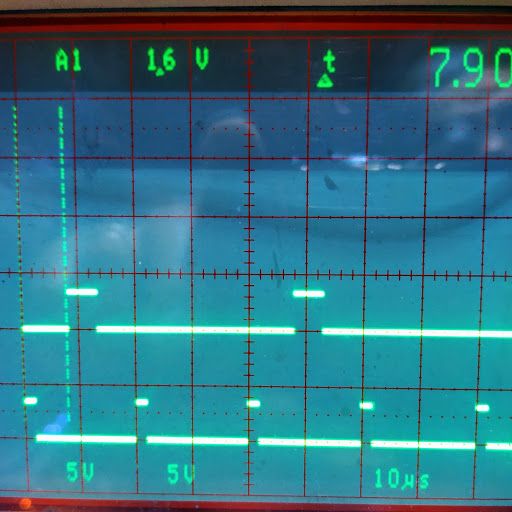

In the attached first picture, the top trace is the duration of the interrupt routine (level is high while in the routine), the bottom trace is channel 3 of TIM2 as PWM (2us every 20us), channel 1 of TIM2 update event being used as the TRGO source for the ADC. 7,9us is the conversion time from update event.

I would have expected having twice the number of conversions and interrupt calls (one per timer pulse).

I am currently using the obvious workaround that is: speed up the counter by reducing the divisor.

Has anyone noticed the behavior I am describing ?

Thanks

Solved! Go to Solution.

- Labels:

-

ADC

-

STM32F3 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-05 11:29 PM

Thanks for your thoughts Clive, found it:

I had specified twice the count of DMA items, the interrupt is actually a "DMA finished" interrupt and is only called once all the items are transfered.

The "reason" for specifying twice the count is that to setup the DMA and start the ADC, I was calling HAL_ADCEx_MultiModeStart_DMA and specifed the size of the buffer in terms of uint16_t as if it where for a single channel DMA, the second argument of HAL_ADCEx_MultiModeStart_DMA is a uint32_t* which should have given me a clue that a count of 32 bit words was expected for DMA in dual simultaneous mode.

Specifying twice the count made the DMA clobber the memory after the buffer, ouch!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-04 02:27 PM

Perhaps look at the sample time you've picked in terms of ADC clocks, and how many samples you're doing.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-05 11:29 PM

Thanks for your thoughts Clive, found it:

I had specified twice the count of DMA items, the interrupt is actually a "DMA finished" interrupt and is only called once all the items are transfered.

The "reason" for specifying twice the count is that to setup the DMA and start the ADC, I was calling HAL_ADCEx_MultiModeStart_DMA and specifed the size of the buffer in terms of uint16_t as if it where for a single channel DMA, the second argument of HAL_ADCEx_MultiModeStart_DMA is a uint32_t* which should have given me a clue that a count of 32 bit words was expected for DMA in dual simultaneous mode.

Specifying twice the count made the DMA clobber the memory after the buffer, ouch!

- G431RBT6 - Interfacing timer and compare output timer have rather fluctuation timings in STM32 MCUs products

- inconsistent behaviour in TIMER and CCxR interrupt in STM32 MCUs products

- ADC Sampling Does not look correct NUCLEO-G474RE in STM32 MCUs products

- Delay of interfacing timer is rather inconsistent in STM32 MCUs products

- COM update interrrupt is delayed 1.3us in STM32 MCUs products