- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32F767ZI could not remapped to internal SRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F767ZI could not remapped to internal SRAM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-29 01:55 AM

Hi folks, I have tried to run my complete program out of internal SRAM to speed up the IRQs

but if I come to svc 0 it fails

prvPortStartFirstTask:

20005ee0: ldr r0, [pc, #32] ; (0x20005f04)

20005ee2: ldr r0, [r0, #0]

20005ee4: ldr r0, [r0, #0]

20005ee6: msr MSP, r0

20005eea: mov.w r0, #0

20005eee: msr CONTROL, r0

20005ef2: cpsie i

20005ef4: cpsie f

20005ef6: dsb sy

20005efa: isb sy

20005efe: svc 0

20005f00: nop

20005f02: movs r0, r0

20005f04: stc 0, cr14, [r8, #-0]

693 __asm volatileWhat I did successfully:

- setting up my openocd for RAM by eclipse with some additional init commands

monitor reset halt

monitor mww 0x40023c08 0x08192a3b

monitor mww 0x40023c08 0x4c5d6e7f

monitor mww 0x40023c18 0x80008000

monitor mdw 0x40023c14

monitor mwb 0x40023c14 0xFE- new SRAM linker file

+LDSCRIPT = STM32F767ZITx_SRAM.ld- startup assembler without copy FLASH to RAM

@@ -79,6 +79,8 @@ Reset_Handler:

/* Copy the data segment initializers from flash to SRAM */

movs r1, #0

+ ldr r2, =_sbss

+ b LoopFillZerobss

b LoopCopyDataInit

CopyDataInit:- erase complete FLASH to avoid any valid vector tables

- set CORTEX M7 vectortable to SRAM @ 0x20000000

------------------------- Src/system_stm32f7xx.c ----------------------------

index 1a362bd..66b7420 100644

@@ -91,7 +91,7 @@

/*!< Uncomment the following line if you need to relocate your vector Table in

Internal SRAM. */

-/* #define VECT_TAB_SRAM */

+#define VECT_TAB_SRAM

#define VECT_TAB_OFFSET 0x00 /*!< Vector Table base offset field.

This value must be a multiple of 0x200. */

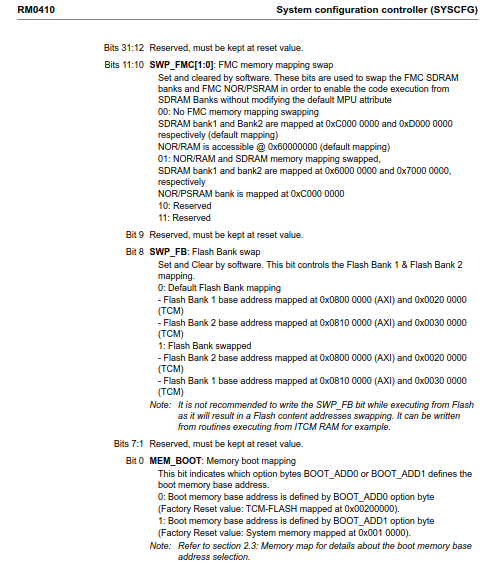

/******************************************************************************/And then I want to remap the SYSCFG memory remap register (SYSCFG_MEMRMP)

but there is no option to do at STM32F7xxxx :pouting_face:

This is the SYSCFG_MEMRMP

Why setting the Vector Table Offset Register is not enough and I have to remap hardware?

Why the SRAM remap option of STM32F4xxxx (see RM401 7.2.1) was removed at STM32F7xxx ?

Alle the core 210MHz speed is lost by 7 wait states for flash because on push and pop of IRQ the ITCM has to fetch twice the I-Cache with 7 wait states.

Looks like the STM32F7xxx is not an IRQ performer without any external RAM

Any ideas how to use this VIDEO RAM to execute IRQ handlers?

- Labels:

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-29 09:24 AM

ITCMRAM is AT ZERO, you don't need to remap it. Both ITCM and DTCM RAM should permit instruction reads

The SCB->VTOR pointing to zero should point to the ITCMRAM, and functionality should be demonstrable.

Up vote any posts that you find helpful, it shows what's working..

- Necleo-STM32F767ZI board fails on example "LwIP_HTTP_Server_Netconn_RTOS" in STM32 MCUs Boards and hardware tools

- STM32H745ZI: About the affect to ITCM after remaping internal flash to address 0x00000000 in STM32 MCUs products

- I2C LOOP BACK TEST in STM32 MCUs products

- XCP internal error: timeout expired' error during for STM32F767ZI on MATLAB Simulink in STM32 MCUs Motor control

- Can't receive any CAN data on STM32F303CCT6 in STM32 MCUs products