- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32F746 QSPI: problem with Flash ROM(Winbond W25...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F746 QSPI: problem with Flash ROM(Winbond W25Q16JV)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-16 06:33 AM

I have a problem with QSPI. I try everything, but program doesn't work.

I am using STM32F746 series MCU and I am trying to interface with a quad spi memory from Winbond (W25Q16JV).

I am following the example found in this location:

(I modified some interface like STM32F769⇒STM32F746)

STM32Cube_FW_F7_V1.15.0\STM32Cube_FW_F7_V1.15.0\Projects\STM32F769I_EVAL\Examples\QSPI\QSPI_ReadWrite_DMA\Src

So far, I have been able to enable writing by executing 06h(Write enable) command and pool for the QE bit setting(set to be 1) by using command 31h(Register-2 Write).

This seems to work.

But, I read the QE bit using command 35h(Register-2 Read), QE bit never be 1.

Could someone know this solution? I want to get how to set QE bit setting to be 1.

My enviroments

1) MCU:STM32F746

2) Flash ROM:Winbond (W25Q16JV)

uint8_t ucRegister2;

static void QSPI_QuadEnableCfg( void )

{

QSPI_CommandTypeDef sCommand;

QSPI_AutoPollingTypeDef sConfig;

/* Read Volatile Configuration register --------------------------- */

sCommand.InstructionMode = QSPI_INSTRUCTION_1_LINE;

sCommand.Instruction = 0x35/* Status Register-2 Read */;

sCommand.AddressMode = QSPI_ADDRESS_NONE;

sCommand.AlternateByteMode = QSPI_ALTERNATE_BYTES_NONE;

sCommand.DataMode = QSPI_DATA_1_LINE;

sCommand.DummyCycles = 0;

sCommand.DdrMode = QSPI_DDR_MODE_DISABLE;

sCommand.DdrHoldHalfCycle = QSPI_DDR_HHC_ANALOG_DELAY;

sCommand.SIOOMode = QSPI_SIOO_INST_EVERY_CMD;

sCommand.NbData = 1;

/* Read Volatile Configuration register --------------------------- */

if (HAL_QSPI_Command(&QSPIHandle, &sCommand, HAL_QPSI_TIMEOUT_DEFAULT_VALUE) != HAL_OK)

{

Error_Handler();

}

if (HAL_QSPI_Receive(&QSPIHandle, &ucRegister2, HAL_QPSI_TIMEOUT_DEFAULT_VALUE) != HAL_OK)

{

Error_Handler();

}

/* Enable write operations */

QSPI_WriteEnable(&QSPIHandle);

sCommand.Instruction = 0x31;

ucWriteData = ucRegister2 | 0x02;/* QUAD ENABLE */

if (HAL_QSPI_Command(&QSPIHandle, &sCommand, HAL_QPSI_TIMEOUT_DEFAULT_VALUE) != HAL_OK)

{

Error_Handler();

}

if (HAL_QSPI_Transmit(&QSPIHandle, &ucWriteData, HAL_QPSI_TIMEOUT_DEFAULT_VALUE) != HAL_OK)

{

Error_Handler();

}

/* 40ms Write Status/Configuration Register Cycle Time */

HAL_Delay( 1000 );

sCommand.Instruction = 0x35/* Status Register-1 Read */;

if (HAL_QSPI_Command(&QSPIHandle, &sCommand, HAL_QPSI_TIMEOUT_DEFAULT_VALUE) != HAL_OK)

{

Error_Handler();

}

if (HAL_QSPI_Receive(&QSPIHandle, &ucRegister2_check, HAL_QPSI_TIMEOUT_DEFAULT_VALUE) != HAL_OK)

{

Error_Handler();

}

}

Solved! Go to Solution.

- Labels:

-

QSPI

-

STM32F7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-20 01:54 AM

Dear Andreas,

Thenk you for your answer.

I have solved!!!

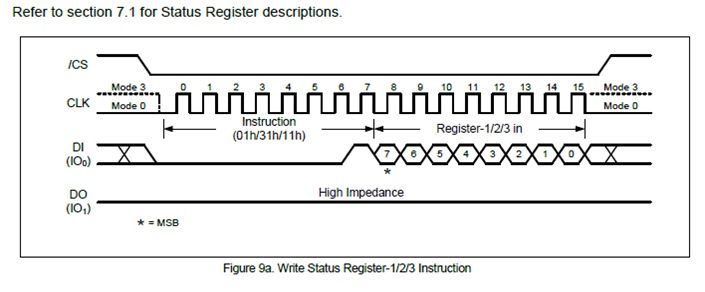

I confirmed that using the command 01h am been able to set the QE bit (Register-1 and Register-2 write at the same time).

I do not know that not be able to set by the command 31h.

I could not find such a description in the manual.

Best Regards,

Kunihiko

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-16 11:26 AM

What does this "This seems to work." actually mean? Did you check WEL was successfully set (by reading the status register) or do you merely think it should be set?

There a lot of other registers and the chip id. Can you actually read all of them and do you get sensible values? Check in particular the protection settings, i. e. SRP, SRL, and the status of the WP pin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-16 05:15 PM

Dear Andreas,

Thenk you for your answer.

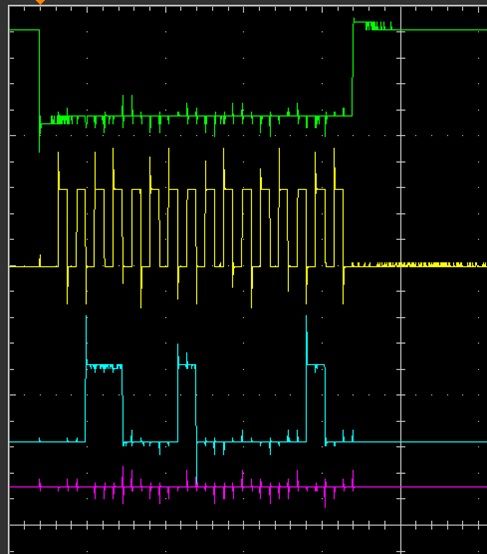

"This seems to work." means I check the signal of the command31h(Register-2 Write) on a oscilloscope.

specification is below.

>>Did you check WEL was successfully set (by reading the status register) or do you merely think it should be set?

⇒Yes, I have been checked WEL by reading the Status Register-1 and polling it until ON.

codes are below.

static void QSPI_WriteEnable(QSPI_HandleTypeDef *hqspi)

{

QSPI_CommandTypeDef sCommand;

QSPI_AutoPollingTypeDef sConfig;

/* Enable write operations ------------------------------------------ */

sCommand.InstructionMode = QSPI_INSTRUCTION_1_LINE;

sCommand.Instruction = WRITE_ENABLE_CMD;

sCommand.AddressMode = QSPI_ADDRESS_NONE;

sCommand.AlternateByteMode = QSPI_ALTERNATE_BYTES_NONE;

sCommand.DataMode = QSPI_DATA_NONE;

sCommand.DummyCycles = 0;

sCommand.DdrMode = QSPI_DDR_MODE_DISABLE;

sCommand.DdrHoldHalfCycle = QSPI_DDR_HHC_ANALOG_DELAY;

sCommand.SIOOMode = QSPI_SIOO_INST_EVERY_CMD;

if (HAL_QSPI_Command(&QSPIHandle, &sCommand, HAL_QPSI_TIMEOUT_DEFAULT_VALUE) != HAL_OK)

{

Error_Handler();

}

/* Configure automatic polling mode to wait for write enabling ---- */

sConfig.Match = 0x02;

sConfig.Mask = 0x02;

sConfig.MatchMode = QSPI_MATCH_MODE_AND;

sConfig.StatusBytesSize = 1;

sConfig.Interval = 0x10;

sConfig.AutomaticStop = QSPI_AUTOMATIC_STOP_ENABLE;

sCommand.Instruction = READ_STATUS_REG_CMD;

sCommand.DataMode = QSPI_DATA_1_LINE;

if (HAL_QSPI_AutoPolling(&QSPIHandle, &sCommand, &sConfig, HAL_QPSI_TIMEOUT_DEFAULT_VALUE) != HAL_OK)

{

Error_Handler();

}

}>>There a lot of other registers and the chip id. Can you actually read all of them and do you get sensible values?

That make sencse. I read the Manufacturer / Device ID(Cmd 90H) and they were correct values.

>> Check in particular the protection settings, i. e. SRP, SRL, and the status of the WP pin.

I have been checked SRP and SRL was been OFF by reading the Status Register-1 and Status Register-2 commands.

Best Regards,

Kunihiko

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-17 07:23 AM

There is one additional point: After trying to program status register 2 (or any other programming instruction), the WEL bit must *automatically* revert to 0. So if it remains 1,

the write hasn't been accepted for some reason. If the write enable command was accepted (i. e. WEL changed to 0) but setting QE to one fails despite correct transmission, I'd suggest you check whether status register 3 is writeable using the *exactly* same setup but using 0x15 and 0x11 instead of the 0x35 and 0x31 instructions. DRV0 and DRV1 can be (re-) programmed several times without causing trouble if the SPI clock is rather slow.

If these bits can be successfully programmed and verified, but QE can't, then ... Well, there are several versions of W25Q16JV around, in particular regarding the QE bit. Althought the datasheet doesn't mention a version with QE permanently set to 0 (or not present at all), it's quite possible such versions exist. The W25Q16 is quite old design, maybe you've got an early revision that does not implement QPI mode at all?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-20 01:54 AM

Dear Andreas,

Thenk you for your answer.

I have solved!!!

I confirmed that using the command 01h am been able to set the QE bit (Register-1 and Register-2 write at the same time).

I do not know that not be able to set by the command 31h.

I could not find such a description in the manual.

Best Regards,

Kunihiko

- Backup SRAM address in STM32F746 ? in STM32 MCUs products

- Steps to enable UDP and TCP protocol ethernet with FreeRTOS LWIP in STM32F746 Discovery board in STM32 MCUs Embedded software

- Error: Problem occured while trying to connect in STM32CubeProgrammer (MCUs)

- Is there a way to change the autogenerated Error_Handler() from cubeMX? in STM32 MCUs products

- STM32F746-Disco, how do I enable ethernet and ping the kit? in STM32 MCUs products