- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Can STM32 read external FIFO through the FSMC inte...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can STM32 read external FIFO through the FSMC interface?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-15 05:47 PM

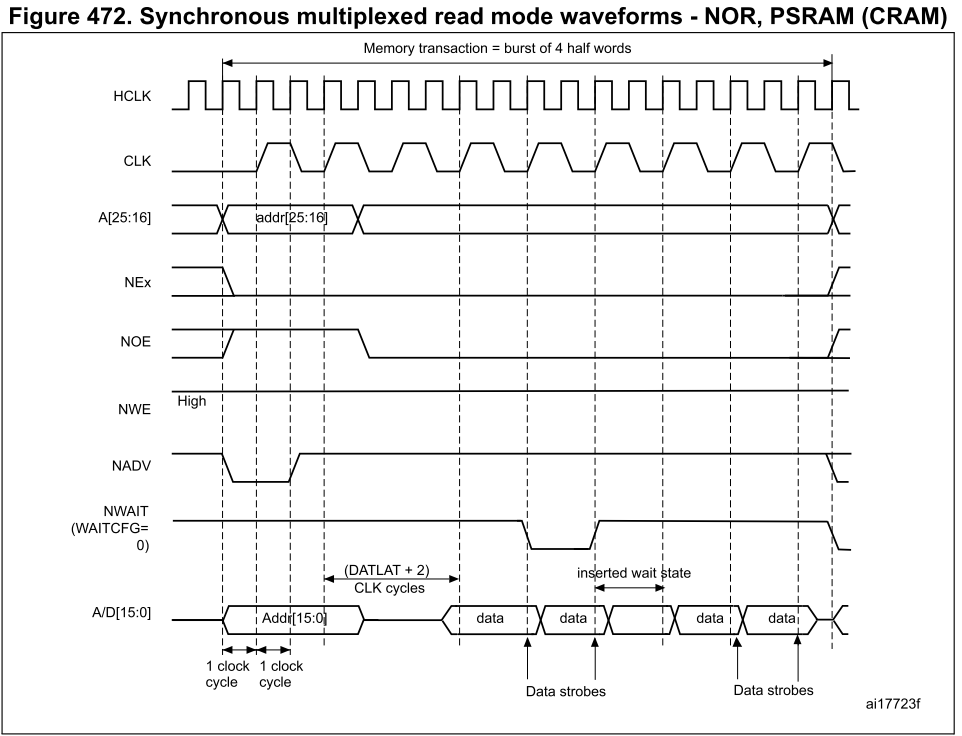

I want to use FSMC to read external FIFO implemented in an FPGA. Since there is no mode of FSMC that can match FIFO interface exactly, so I want to use the modified synchronous multiplexed PSRAM mode.

The plan is like this

A[25:16]: Ignored, don't connect to FIFO;

NEx, NOE, NADV: Implement a simple logic in FPGA that when NEx is valid and the NADV is data valid, connect the inverted NOE to the RD port of FIFO;

NWE: ignored, only read operation is needed;

D[15:0] : Connect to the output data port of FIFO;

There may be also some logic in FPGA to adjust the timing between NOE and D[15:0], but that is not a big problem.

What I want to ask is

- Is this plan feasible? What should I take care of when implement it?

- How can I extend the data burst length as long as possbile? Since there are 2048x16bit in one frame, I want to read them all in one burst if possible.

- Labels:

-

FMC-FSMC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-16 09:52 PM

It's hard to say without knowing about the FIFO signals and their timing requirements.

- can Ewarm project be opened in Keil or CubeIDE ? in STM32 MCUs Boards and hardware tools

- problem reading data from SCD30 with NUCLEO-L476RG in STM32 MCUs products

- Adafruit TFT 1.8'' v2 shield support for Nucleo STM32L476 in STM32 MCUs Embedded software

- STM32L4P5VGT - CDC, MSC and Pen Drive Support on USB in STM32 MCUs Embedded software

- Touchgfx base classes on external flash memory in STM32 MCUs TouchGFX and GUI