- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Misalignment between reference manual and low leve...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Misalignment between reference manual and low level driver on STM32L011D3

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-24 05:24 AM

Hello.

I'm working on a STM32L011D3.

I've created the project using the latest version of MXCube, and I'm using low level driver to manage the hardware resources.

I've configured TIM21 to generate a PWM on PA9 (Output channel 2), and it works correctly.

To protect the power stage, a current signal is provided trough a sense resistor.

This signal is conncted to COMP2_INP (PA7). This comparator should force off the PWM output if the current is too high, trought the ETR signal.

Looking into "STM32L0 HAL and Low Layer drivers" manual (UM1749 - DocID026232 Rev 6), I've found the LL_TIM_OC_EnableClear function that enables the behavior I was looking for.

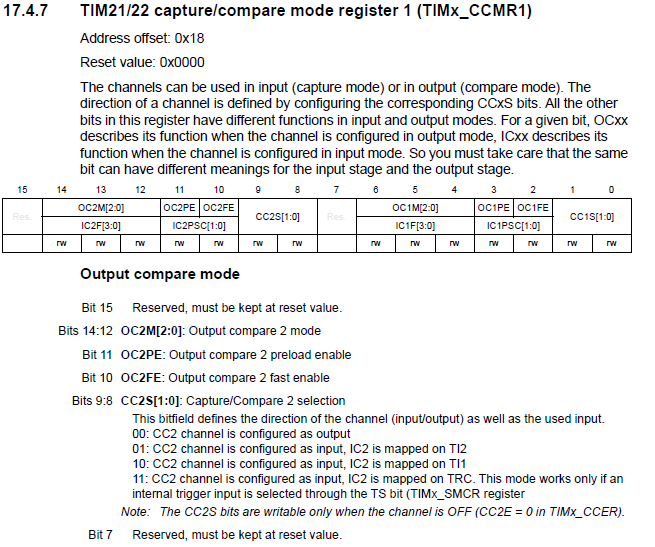

If i'm correct, this function sets the bit 15 of TIM21_CCMR1 register, that in the Refernce manual (RM0377 - DocID025942 Rev 😎 is declared "Reserved, must be kept at reset value."

So the question is: Is the Low level driver correct and in the manual there is something missing, or that bit must be left clear and the driver si doing something wrong?

thank you in advance.

Paolo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-24 06:31 AM

Pretty sure LL_TIM_OC_EnableClear() doesn't validate input parameters, or viability on all TIM, especially those supporting a subset of the maximal configuration.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-24 07:35 AM

Thank you, Clive.

I agree to you, but, the strange thing is that the functionality is described in the reference manual, the only thing that is missing is the bit description in the timer registers paragraph.

In the stm32l011xx.h file (that is specific for this uc) the bit is exposed via this define, even if it is undocumented:

#define TIM_CCMR1_OC2CE_Pos (15U)

#define TIM_CCMR1_OC2CE_Msk (0x1UL << TIM_CCMR1_OC2CE_Pos) /*!< 0x00008000 */

#define TIM_CCMR1_OC2CE TIM_CCMR1_OC2CE_Msk /*!<Output Compare 2 Clear Enable */Calling the function that uses the defines above reported, it makes all work correctly...

For that reasons I thought that it was a documentation issue... my intention was to report the matter for a possible correction and obtain, in the meanwhile, confirmation of my hypothesis, just to be sure I'm using the timer in the correct way.

Just to complete the information, this is the screenshoot of the manual:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-29 11:20 PM

So, please, is there anybody that knows if the bit 15 of TIM21_CCMR1 register can be used to clear the OC2REF signal on an external event, as written in the description paragraph, or it must be left clear, as written in the register description?

Thank you.