- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32H7 DMA and different memories

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H7 DMA and different memories

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-19 09:36 AM

Hello,

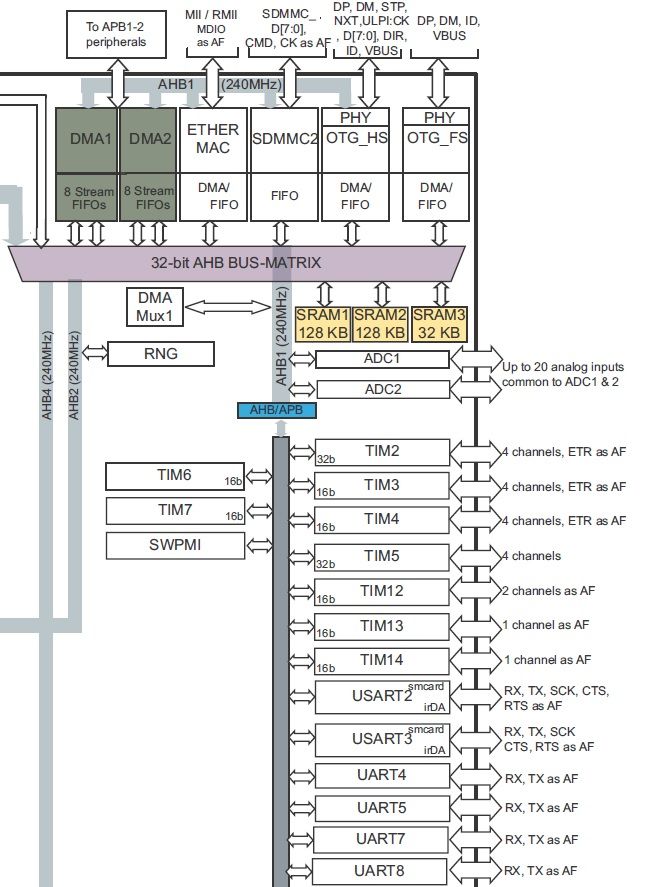

I have been tasked recently with porting some code from another microcontroller into the STM32H7. Right now I am taking care of the UART communication and some parts around that. And I would like opinions and advice about some things if possible.

Since the architecture is quite a bit different and the clock is so high, I wanted to see how can I increase performance on previous implementations. Some targets will do quite a bit of math processing, while some will mostly communicate with multiple targets.

I've been looking at the documentation of the memories and DMA as well as AN4891.

Of note is that one target will be using ethernet.

Previous implementations of UART communication simply had a TX and RX interrupt sending/filling a buffer. Some had some DMA for TX.

My idea is to have:

CPU only using DTCM if possible for data.

CPU using ITCM for most (all?) ISRs.

CPU running code from flash with cache on.

This is to avoid cache misses which can happen (always?) during interrupts and to avoid wait-states and latency.

Then for UART communications (can be multiple UARTs) I would use DMA if needed/possible. The thing is, if I use code like the example "MDMA_GPDMA_Triggering" that would mean that the DTCM RAM would be frequently be accessed to store a few bytes and I am a bit worried about that. I was wondering if it was better to have a buffer in DTCM transfered into SRAM1 (maybe by MDMA), this would be really fast once, and then DMA would transfer to UART as the peripheral requested. And vice-versa for receiving data, the processor would request data from SRAM1 as needed to process.

If I needed big buffers that would not fit well in DTCM this might also help.

is this too far fetched?

Solved! Go to Solution.

- Labels:

-

DMA

-

STM32H7 Series

-

UART-USART

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-19 11:16 AM

Presumably the USART aren't going to route to the DTCMRAM via DMA, much better to localize that traffic into SRAM1,2 and 3

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-19 11:16 AM

Presumably the USART aren't going to route to the DTCMRAM via DMA, much better to localize that traffic into SRAM1,2 and 3

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-20 07:05 AM

Hello Clive,

Thanks for the answer. You are correct, though, as the example "MDMA_GPDMA_Triggering" shows that it is possible to send DTCM to UART by using the MDMA with DMA. They can be connected together (not the correct word but it should be enough to explain).

I am still inclined to do, as you say, to use D2 RAM to feed the UART as it seems better anyway.

- STM32 NUCLEO G071RBT6 Memory map in STM32 MCUs Boards and hardware tools

- Touchgfx base classes on external flash memory in STM32 MCUs TouchGFX and GUI

- Delay in SPI Transfer with STM32H7 in STM32 MCUs products

- Use flash memory area between (origin + length) and Wireless Coprocessor Binary start address in STM32 MCUs Wireless

- Confusing use of decimal separator/thousands separator in doc in STM32 MCUs TouchGFX and GUI