- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- LSM6DSM: Unreliable SPI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LSM6DSM: Unreliable SPI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-19 08:29 AM

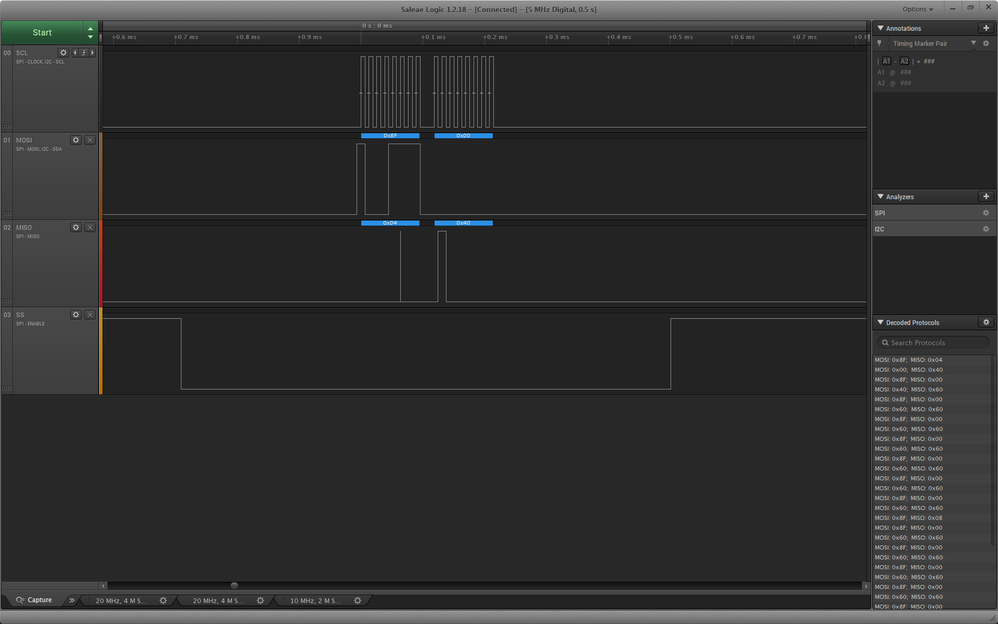

Hi all, I'm trying to bring up an LSM6DSM (MKI189 dev board) via SPI using a Nucleo and the STM C libraries for it. I've had some luck but I'm getting extremely unreliable SPI communication ( MISO line specifically ). For starters when I read the WhoAmI register I sometimes read 0x6A as expected but I read a number of other things as well ( 0x60, 0x40, 0x44 ) are common.

I've been trying to use the logic analyzer to figure out what's going on and I've noticed that depending on how the board feels having the Logic Analyzer (Saleae) attached can make things better or worse. I have my code reading the register every 100ms and I'll try disconnecting/reconnecting the harness from the logic analyzer. Sometimes plugging it in make it impossible to read the correct value and sometimes unplugging it makes it impossible. During the transition of plugging in/unplugging it almost always is able to read the correct value. I suspected noisy lines at first but I'm running at 20kHz now.

Does anyone have any suggestions on where to look to debug this?

Quick edit: I2C seems to work just fine.

- Labels:

-

INEMO-Inertial Modules

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-19 09:28 AM

Change the sampling edge or clock polairty and make sure you are using 3 or 4 wire SPI mode. (CPOL/CPHA)

Oscilloscope should be used before going digital logic analyser which won't tell you for example if some lines are open-drain.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-19 09:54 AM

I've tried in both SPI mode 0 and 3 which are the two it supports. I'm not sure how to verify 3/4 wire mode when the communication is so unreliable. The host STM32 is configured for 4 wire. I unfortunately don't have access to a scope right now.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-19 10:11 AM

Older MEMs boot up in 3 wire, the MISO line not being activated, hence you can't really read anything steady.

Writing blindly some control register bit to activate 4 wire mode was needed.

In 3 wire mode, you need to short MISO and MOSI of STM32 AND disable MOSI when reading (GPIO.MODER register to flip)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-20 06:20 AM

Looks like this MEMs defaults to 4-wire but I tried 3 wire and writing that register regardless. Still the same behviour. Any other thoughts?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-20 06:40 AM

I just noticed something new. If I remove the MISO connection between the STM32 and the LSM then I see the LSM outputting the correct 0x6A response very consistently. It's almost like the STM32 is not allowing the LSM to drive the line the way it needs to.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-20 10:44 AM

ok, then in debug mode, put a breakpoint and look at the GPIO and SPI HW registers.

You can even manually change them and let the code continue...

Check HW registers bit by bit against the reference manual register description and find the flaw.

- LSM6DSM - Inquiry regarding 12-sec periodic noise in MEMS (sensors)

- LSM6DSM interface with STM32L476 in Sensortile board in MEMS (sensors)

- LSM6DSM- Incorrect Accel Data on high ODR using FIFO in MEMS (sensors)

- LIS3DH consuming high current at interrupt in MEMS (sensors)

- IMU LSM6DSM onboard Filters in MEMS (sensors)