- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Reduce power consumption STM32L4

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Reduce power consumption STM32L4

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 03:26 AM

Hello there,

I am developing a FreeRTOS based application using STM32L452 MCU. I am looking for a way, to reduce the power consumption in the idle intervals of the processors work. When reviewing the sleep modes, it occured to me that the MCU might be unresponsive to external events or even lose context (MCU reset), which is not fit in this RTOS running application.

I thought then that I could simply reduce the HCLK frequency by playing with the PLL registers. The problem here is that the systick timer will get altered, and I really need it to stay with its regular timebase (1 ms). I checked either it is possible to clock the Systick timer from other sources, but it seems like its only HCLK and HCLK / 8. The datasheet says it is calibrated for this value.

I would appreciate some suggestions on this topic.

Lukasz.

Solved! Go to Solution.

- Labels:

-

Power

-

STM32CubeMX

-

STM32L4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-05-10 12:45 PM

There's a project that use LPTIMx as the tick timer: this way you can have FreeRTOS ticks updated even in STOPx modes (it's what you need imho).

Changing SYSTICK prescaler (/1 or /8) is nice if you want to run occasionally faster, but you're generally fine at lower speeds. It offers a limited gain only compared to STOP mode sleep states (ie: sleep @64 MHz ~1.4 mA; sleep @8 MHz ~0.3 mA; while stop2 is lower than ~10uA). Anyway, this exactly what I needed recently. This is my blog post with implementation details on it (changing voltage scaling, flash latency, tuning pll, etc).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 04:10 AM

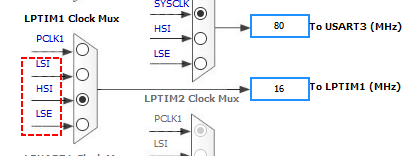

Clock LPTIMER with HSE an use it as systick. Then you can reduce HCLK during sleep.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 04:15 AM

Can't you adapt the SysTick count as you alter the speed.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 04:35 AM

Hello, thank you for answers.

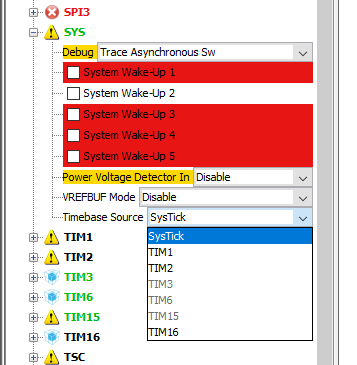

@Uwe Bonnes it seems that it is not possible to use LPTIM as system timebase source:

Also, it seems that the only sources I can use for LPTIM clocking are not precise ones...

@Community member the way I understood the datsheet is that the systick base is factory calibrated for 80 Mhz / 8 usage with this MCU and by altering the base I wont get exact timing?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 04:52 AM

I don't even know that ST sets that constant. Any way ARM suggests providing a default value, but you get to program whatever you want for the period, so the frequency of the CPU and if the ticker fires at 1 KHz or something else is entirely up to you.

The point with the LPTIM is you could use it or the RTC to provide the HAL timebase, you're not tied to SysTick. Even RTOS should be workable with a different periodic IRQ.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 05:04 AM

Ok, now I see the point.

Ideally, I was wondering about such idea: reduce the HSE osc frequency as much as I can (4 Mhz crystals are there, 2 Mhz are probably findable too). In "regular mode" just use PLL abd default settings for 80 Mhz operation with systick. In the "dormant mode" modify the timing registers to clock everything without any PPL, directly from HSE. In that case it would be 2-4 Mhz for the systick and I would have to modify the registers to keep the 1 ms time base (the same for other timers if used). What do you think?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 05:16 AM

The tick interrupt could orchestrate the clock changes. LPTIM might be able to take a low frequency source. LSE can take up to 512 KHz as I recall.

Likely going to have to manually code rather than bang at options in CubeMX.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 05:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 05:51 AM

Or resync system clock on wakeup with RTC.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 05:51 AM

If you are looking to switch to SLEEP low power mode while idle then an active SysTick is not your friend. The FreeRTOS website has a lot of details on running a "tickless" RTOS timebase in order to get the most benefit from SLEEP mode.

The problem is you only sleep for a maximum of the SysTick interrupt period, which isn't very long. You aren't going to see a dramatic difference in power consumption because the core is constantly waking up to handle SysTick interrupts, without actually accomplishing any useful work. If you use the RTOS tickless mode you get the maximum benefit from idling the core while sleeping. The core stays idle until a timeout (scheduled task wakeup) or an external event occurs. The difference is you sleep the core for seconds or even minutes at a time, rather than milliseconds.

RTOS tickless mode also allows you to implement STOP low lower mode if your hardware connections allow for it. That has a dramatic effect on battery life.

And if you do go with dynamic frequency scaling be sure to adjust the core voltage after you drop to a lower clock rate. If you check the data sheets you'll see it makes a difference.

- STM32F4 Current consumption versus clock speed in STM32CubeMX (MCUs)

- Issue with HAL_Init, my board, or my code? in STM32CubeIDE (MCUs)

- How to enter low-power run mode? in STM32CubeMX (MCUs)

- Reduce FMC consumption current in STM32CubeMX (MCUs)

- power consumption stm32l4 in lprun mode in Other tools (MCUs)