- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32 rise/fall shape

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 rise/fall shape

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-02 06:34 PM

Hi, guys. I bought

- STM32F446RE, mbed-Enabled Development Nucleo STM32F4 MCU 32-Bit ARM® Cortex®-M4 Embedded Evaluation Board (NUCLEO-F446RE)

https://www.digikey.com/product-detail/en/stmicroelectronics/NUCLEO-F446RE/497-15882-ND/5347712

- 8MHz ±10ppm Crystal 18pF 80 Ohms HC-49/US

https://www.digikey.com/product-detail/en/txc-corporation/9B-8.000MEEJ-B/887-1233-ND/2207653

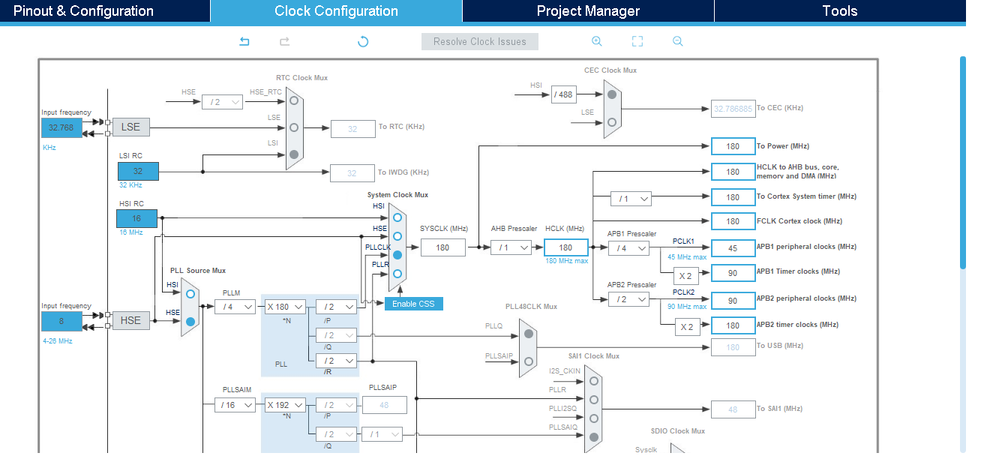

Mostly the internal clock is less accurate than the external crystal. So I'm planning to populate a 8MHz clock to the board.

- If I use the external 8MHz as a clock source, do I get an accurate timing than using the internal high frequency resonator?

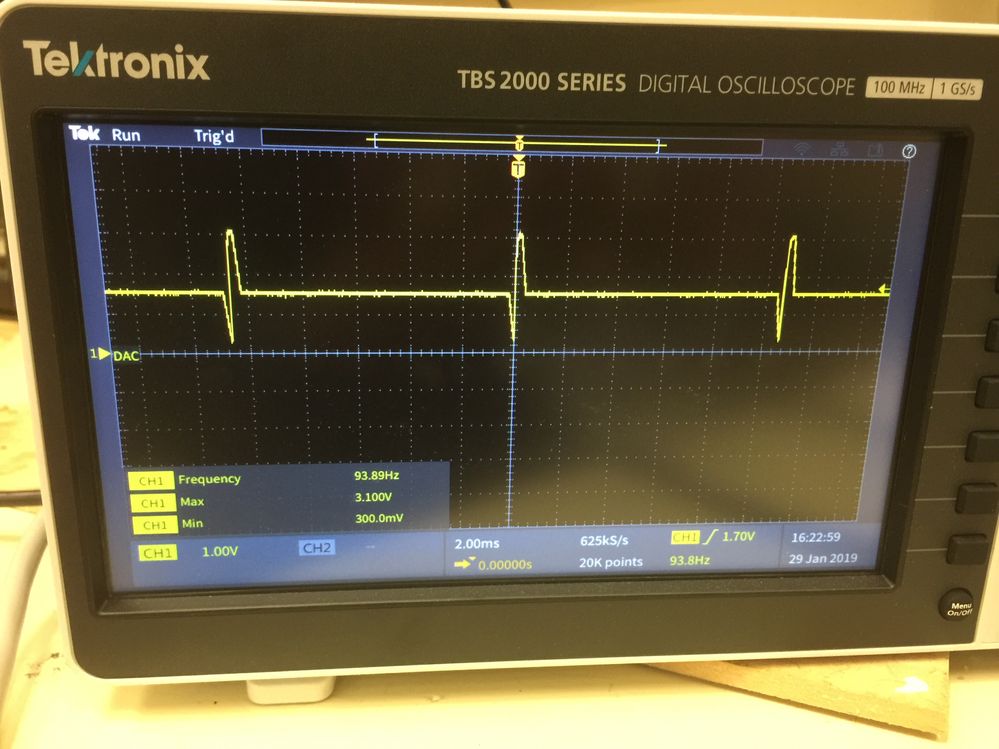

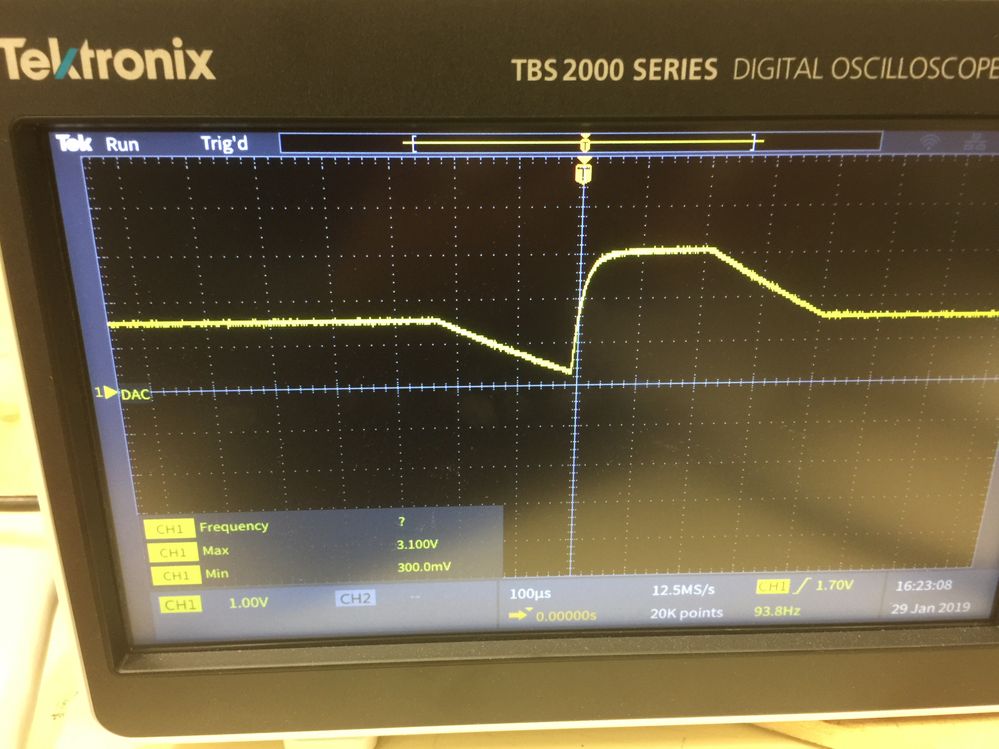

- I noticed the 12-bit DAC of STM32L4 discovery board showed the above result. I tried to toggle 0V ~ 3.3V after 200usec. The waveform was not flat compared to the STM32F4 discovery board's output. Since the STM32L4's APB1 clock is faster than STM32F4's APB1 clock, I thought STM32L4's DAC would do the same job. What is the reason for STM32L4 DAC's output when operating with usec range?

-Thanks!

Solved! Go to Solution.

- Labels:

-

DAC

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-02 09:08 PM

DAC is an analog static structure. Made short for conceptually understanding it's like a resistor ladder with switches to define a voltage ratio, and an optional buffer to lower the output impedence and have a decent slew rate. The DAC itself does not need clocks, only for the controls. The clock defines how fast the DAC requested voltage update can be, or output sampling rate.

Nucleo all pins are available and not tied to any external components.

For DAC outputs (PA4 and PA5 typically) on Discovery, check for schematics and make sure nothing else is impairing the analog DAC on the board.

In the datasheet, you'll find the max slew rate values. DACs are not intended to make square waves, which push-pull digital pins will do well.

Analog outputs usually are implemented by PWMs with external RC filter, which are "cheap" way to have analog signals.

When it must be high frequency analog signal, or when the analog output must be steady when the STM32 is in clock stop mode (static), DAC then shines.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-02-02 09:08 PM

DAC is an analog static structure. Made short for conceptually understanding it's like a resistor ladder with switches to define a voltage ratio, and an optional buffer to lower the output impedence and have a decent slew rate. The DAC itself does not need clocks, only for the controls. The clock defines how fast the DAC requested voltage update can be, or output sampling rate.

Nucleo all pins are available and not tied to any external components.

For DAC outputs (PA4 and PA5 typically) on Discovery, check for schematics and make sure nothing else is impairing the analog DAC on the board.

In the datasheet, you'll find the max slew rate values. DACs are not intended to make square waves, which push-pull digital pins will do well.

Analog outputs usually are implemented by PWMs with external RC filter, which are "cheap" way to have analog signals.

When it must be high frequency analog signal, or when the analog output must be steady when the STM32 is in clock stop mode (static), DAC then shines.

- How to connect microsd card in stm32f407 in STM32 MCUs products

- USB project example in STM32 MCUs products

- can Ewarm project be opened in Keil or CubeIDE ? in STM32 MCUs Boards and hardware tools

- STM32 SD Card write multi block in STM32 MCUs Boards and hardware tools

- STM32 NUCLEO G071RBT6 Memory map in STM32 MCUs Boards and hardware tools