- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- spi master slave communication

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

spi master slave communication

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-22 06:44 AM

Hello every one,

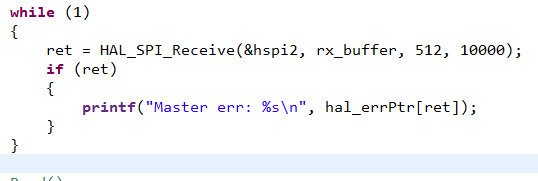

I am trying to communicate spi master and slave with two discovery boards

In my case stm32l152rc is master and stm32f407vg is slave..

When i am sending from master to slave it's receive complete data but when am sending slave to master data it's recived but only 1st byte only in my buffer.

when i am debug slave code at that time slave completely put all data in to DR resister and when master not enble it's clock it's show timeout,too so there is problem whit master side or slave side i cant identify...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-23 04:43 AM

If the bitrate is high, polling-based transmit in slave may be too slow to be able to store new data in DR in timely manner. You may need to use DMA, or decrease bitrate significantly.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-23 05:24 AM

Hi JW,

Thanks for your reply, I am using stm32 l152rc as master with 125KHZ frequency of SPI and I am using interrupt in my slave stm32f407ve but not get the proper output. Even I am trying to make f4 as master and l1 as a slave but facing same problem.

I did not understand exactly what happen there.

In polling mode and interrupt mode nothing change in output

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-23 06:59 AM

Check if the respective GPIO pins are set properly. How do you manage NSS in the slave?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-23 07:03 AM

Hi JW,

i am using software NSS in slave and master to slave transmit work properly but when I am trying slave to master at that time facing this problem

I am also try to use DMA but not working

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-23 09:15 AM

I took software NSS. So its 3 wire communication.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-23 11:10 AM

I would try first SPI 4 wire intrface. Master driving NSS as GPIO, Slave using NSS as EXTI interrupt,to know when the data transfer start/stop (SPI could be entirely reset when NSS goes high to resync it). This can prepare the Slave SPI before SCK activity starts, make DMA Cyclical so you don't need to care if the master reads more than needed bytes. No DMA interrupt for slave.

While not perfect, I use MISO and MOSI short outside the STM32 to generate 3 wire interface.

DMA TX and RX shall be set properly. Only the master DMA RX shall have interrupt to detect all clocks were transmitted by master.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-25 05:59 AM

HI KIC8462852 EPIC204278916,

Thanks for your reply as per your advised I tried with NSS with hardware configuration and I archived next step, I still facing problem in master side,

Here I attached some screen shorts can you please help me to solve this problem?

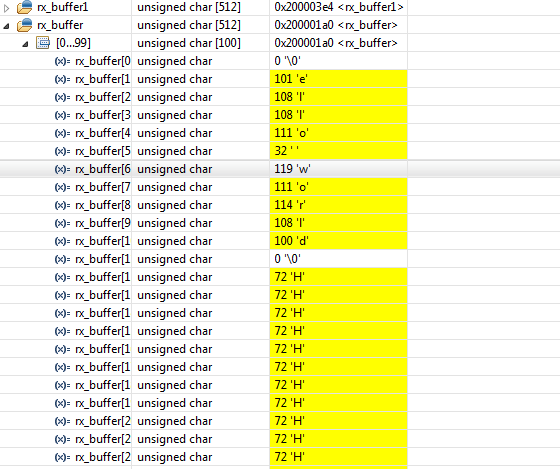

And i have doubt why i received 1st byte in last and received it n times?

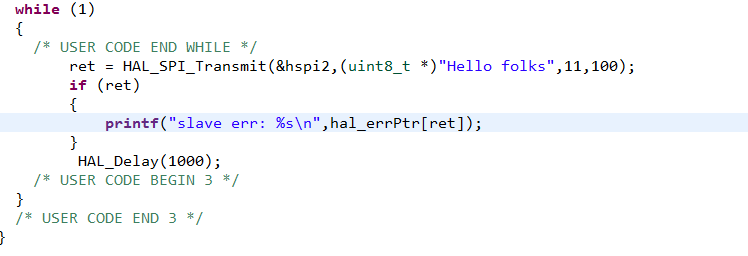

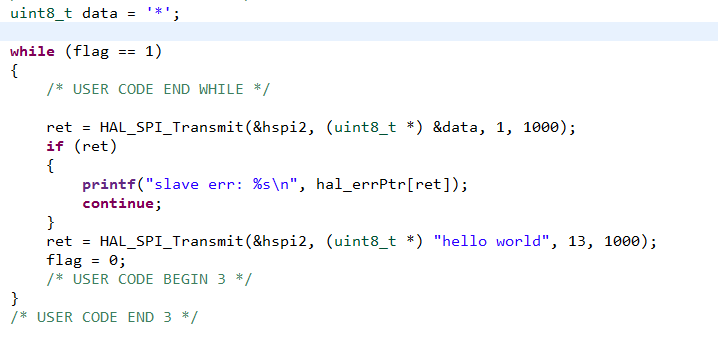

code flow....

received buffer data...