- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- How to implement the missing CC channels and inter...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to implement the missing CC channels and interrupts in low layer API?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-03 11:37 AM

Hi

I just started porting a project over to STM32. It does some complex stuff with timers. First I found out the the HAL doesn't support my usage of one pulse mode in timers. So I went for the LL API which I liked on first sight.

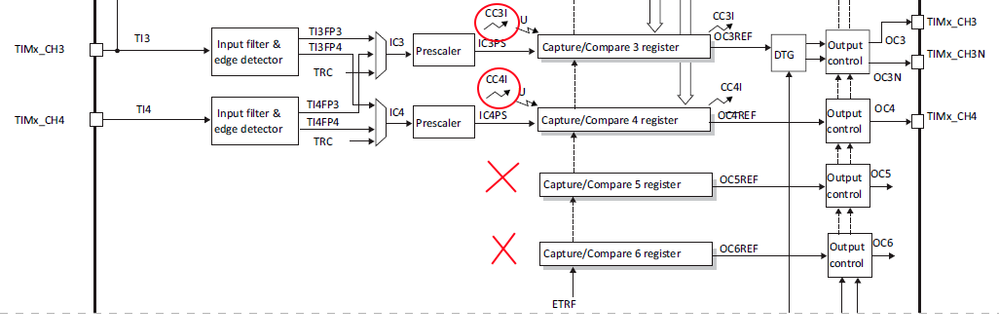

Now I found out that the LL API only implements 4 of 6 capture compare channels of the advanced timer 1 of STM32F3xx.

I need at least 5 CC channels. What can I do to get the rest of the CC channels?

I started adding the missing functions and constants but I suppose I won't get it to run because I also need the corresponding interrupts and other functionality so I will probalby hit something not implemented in C.

Best Regards

Michael Bürschgens

Solved! Go to Solution.

- Labels:

-

STM32F3 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-04 08:11 AM

Hello,

The channel 5 and 6 do not have an interruption or DMA request.

And about the status register TIMx_SR, the bit of this register is set when the counter matches the corresponding compare value even if the interruption is disabled.

Best Regards,

Imen.

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-03 12:00 PM

> I will probalby hit something not implemented in C

You mean, something not implemented in the Cube/LL "library"?

For anything more complex than the basic functionality, it's probably better to avoid any "library" and program directly at the register level. Simply read the TIM1 chapter in RM and follow the registers descriptions.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-03 12:11 PM

You did not tell us exactly which STM32F3xx you use, so I just looked at the TIM1/TIM8/TIM20 chapter of RM0316 Rev.8, and noticed, that there are no *interrupt enable flags* for channels 5 and 6 mentioned in TIMx_DIER , although there are respective *interrupt flags* in TIMx_SR (CC5IF and CC6IF).

I don't have a 'F3xx at hand to try now, but it may as well mean that these channels can't trigger an interrupt.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-03 12:30 PM

The MCU is STM32F302x8 but the *_ll_tim.h is the same for all. The datasheet mentiones the timers and their registers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-03 12:33 PM

With "not implemented in C" I mean that maybe some necessary calls are not implemented in the binding layer between compiled code and hardware. I don't know the right terminology. I mean what the linker links to.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-03 01:23 PM

You are right. There are some registers missing. So the last two CC channels are almost useless. What a pitty. :(

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-03 11:04 PM

"not implemented in the binding layer between compiled code and hardware"

I think you do not understand the concept of bare metal embedded programming. The timer is just a block of registers on the memory map. You can access these via a pointer and an operation with the correct width. That is a limit of the hardware.

Only complex operating where the ARM Cortex does not have instructions for will the linker map to a library. Floating points for example. Reading and writing timer register is not one of those.

Take a look inside the hal or hal_ll to see there is no "binding layer".

I don't think there are any language features of C unavailable, C++ however...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-04 08:11 AM

Hello,

The channel 5 and 6 do not have an interruption or DMA request.

And about the status register TIMx_SR, the bit of this register is set when the counter matches the corresponding compare value even if the interruption is disabled.

Best Regards,

Imen.

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-04 01:27 PM

Thanks for the clarification, Imen.

It's a pity they don't. I also don't get the purpose of OC6 (i.e. the output control unit of channel 6), and in TIM20, also OC5...

JW

- LPBAM I2C data buffer using NUCLEO-U575ZI-Q in STM32 MCUs products

- STM32H5 SPI DMA LL Transfer Timing Issue in STM32 MCUs products

- PWM behavior when changing deadtime during operation in STM32 MCUs Motor control

- STM32H7 ADC1 and ADC3 errors in STM32 MCUs products

- USB Type-C IC suggestion in STM32 MCUs Other solutions