- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32H7 DMA: what are the destinations for dmamux1...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H7 DMA: what are the destinations for dmamux1_evt[3..15] signals?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-28 01:44 PM

There is the Figure 80 "DMAMUX block diagram" in the STM32F743 Reference Manual (RM0433), which shows that there is 'm' number of dmamux_evt signals, where 'm' is 16 for DMAMUX1 (the number of DMAMUX1_CmCR channels).

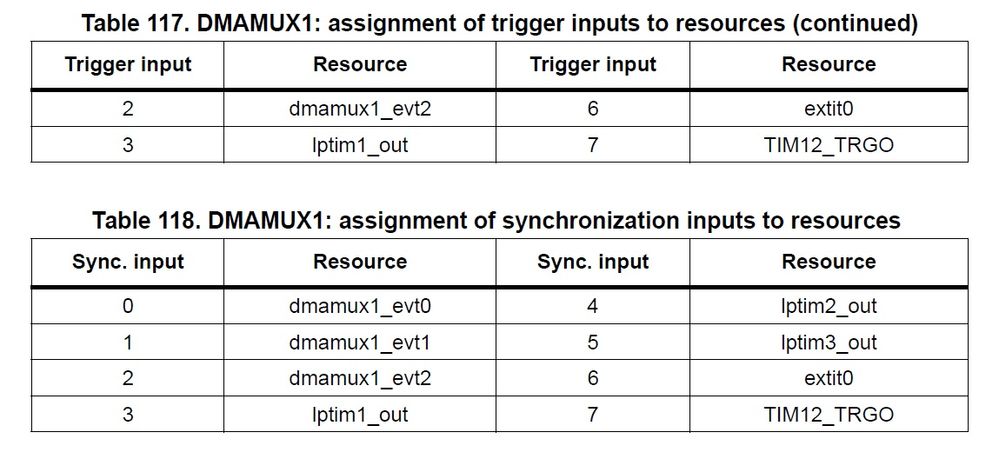

The Manual only describes the destinations for dmamux1_evt[0..2] signals in the Table 117 "DMAMUX1: assignment of trigger inputs to resources" and Table 118 "DMAMUX1: assignment of synchronization inputs to resources", while it does not describe the destinations of dmamux1_evt[3..15] signals.

My question is: what are the destinations of dmamux1_evt[3..15] signals, where do they come to as inputs after leaving the DMAMUX1 block?

- Labels:

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-28 02:41 PM

I think this is an IP macro cell, indications are only four events are wired to anything, and dead nodes have been eliminated.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-01 06:19 AM

Clive, just to clarify, do I correctly understand that evt[3..15] are connected to virtually nowhere? And by "four" you mean three evt[0..2]?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-01 08:15 AM

Actually I think it's eight inputs, didn't notice there were two columns

Up vote any posts that you find helpful, it shows what's working..

- G431RBT6 - Interfacing timer and compare output timer have rather fluctuation timings in STM32 MCUs products

- STM32H QSPI LL Driver in STM32 MCUs products

- I2C multibus on alternative pins howto or is possible? in STM32 MCUs products

- STM32H745BI SPI port does not start in STM32 MCUs products

- Delay of interfacing timer is rather inconsistent in STM32 MCUs products