- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32 interrupt priority

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 interrupt priority

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-06 07:10 AM

Hi

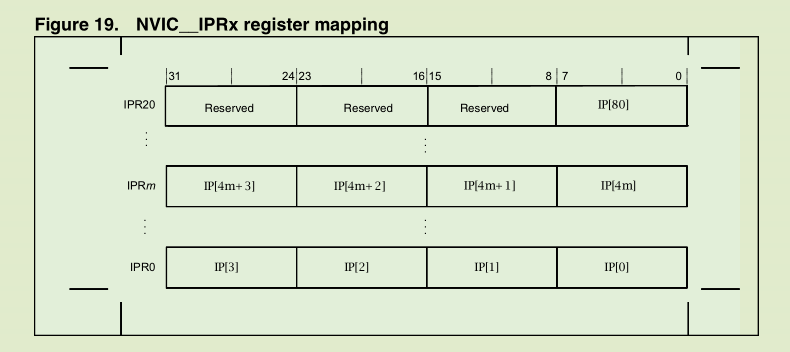

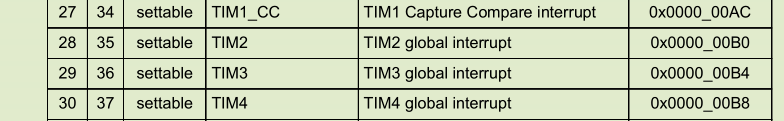

I want to set interrupt priority for TIM3. So I made configuration in NVIC register.But I met some question.the base adress of NVIC in STM32F10xxx Cortex-M3 programming manual is 0XE000E100 ,but in another book STM32F10xxx Cortex-M3 programming manual is 0XE000E000,that really made me confused. the position of TIM3 in the vector table is 29.so which NVIC_IPRx should I use.IPR 7 is right ? and what's its adress ? I'm using assembly language not C language. Thank you.

- Labels:

-

Interrupt

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-06 10:26 AM

Easily confused?

Some of the registers are a bit file, others a byte file, the exact scope of specific silicon depends on the number of interrupts in the table.

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/BHCFCFDB.html

Recognize there are Interrupts and there are System Handlers, the NVIC deals with the former, the Vector table contains both.

>>I'm using assembly language not C language.

Ok, but that shouldn't render you incapable of looking how the CMSIS code exposes/controls the access to the NVIC, and then applying it to the assembler code.

ISER Bit Vector 0xE000E100

ICER Bit Vector 0xE000E180

ISPR Bit Vector 0xE000E200

IPR Byte Vector 0xE000E400

TIM3 would be BIT 29, BYTE INDEX 29, right?

The NVIC base is 0xE000E100

/**

\ingroup CMSIS_core_register

\defgroup CMSIS_NVIC Nested Vectored Interrupt Controller (NVIC)

\brief Type definitions for the NVIC Registers

@{

*/

/**

\brief Structure type to access the Nested Vectored Interrupt Controller (NVIC).

*/

typedef struct

{

__IOM uint32_t ISER[8U]; /*!< Offset: 0x000 (R/W) Interrupt Set Enable Register */

uint32_t RESERVED0[24U];

__IOM uint32_t ICER[8U]; /*!< Offset: 0x080 (R/W) Interrupt Clear Enable Register */

uint32_t RSERVED1[24U];

__IOM uint32_t ISPR[8U]; /*!< Offset: 0x100 (R/W) Interrupt Set Pending Register */

uint32_t RESERVED2[24U];

__IOM uint32_t ICPR[8U]; /*!< Offset: 0x180 (R/W) Interrupt Clear Pending Register */

uint32_t RESERVED3[24U];

__IOM uint32_t IABR[8U]; /*!< Offset: 0x200 (R/W) Interrupt Active bit Register */

uint32_t RESERVED4[56U];

__IOM uint8_t IP[240U]; /*!< Offset: 0x300 (R/W) Interrupt Priority Register (8Bit wide) */

uint32_t RESERVED5[644U];

__OM uint32_t STIR; /*!< Offset: 0xE00 ( /W) Software Trigger Interrupt Register */

} NVIC_Type;

/* Software Triggered Interrupt Register Definitions */

#define NVIC_STIR_INTID_Pos 0U /*!< STIR: INTLINESNUM Position */

#define NVIC_STIR_INTID_Msk (0x1FFUL /*<< NVIC_STIR_INTID_Pos*/) /*!< STIR: INTLINESNUM Mask */

/*@} end of group CMSIS_NVIC */Vector Table entry address VTOR + 0x40 + (29 * 4) -> 0x080000B4

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-06 08:06 PM

A big thank you for your patience

- LWIP STM32, if ethernet cable not connected, tcp server not accepting client connection in STM32 MCUs products

- Delay in SPI Transfer with STM32H7 in STM32 MCUs products

- STM32 UART only working with debugger in STM32 MCUs products

- PSP switches to the handler stack upon function return in STM32 MCUs Embedded software

- STM32L0 LPUART reboot in STM32 MCUs Embedded software