- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32L4 series PLLs?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32L4 series PLLs?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-04 11:27 AM

There seems to be something I don't quite get.

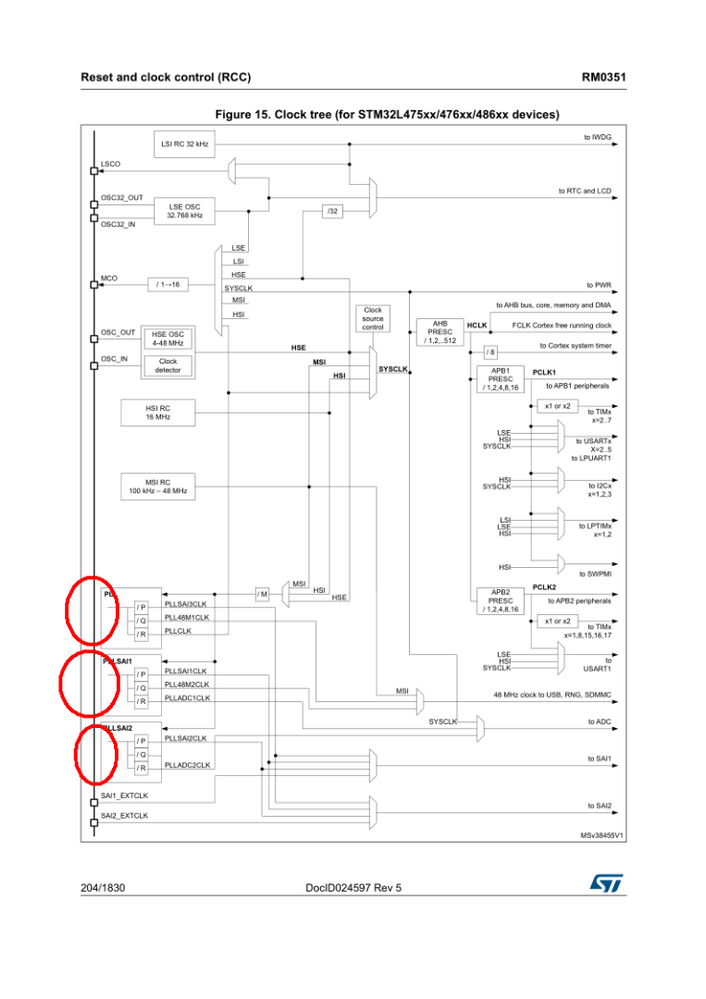

In the reference manual it says 'The PLLs input frequency must be between 4 and 16 MHz.' and 'The selected clock source is divided by a programmable factor PLLM from 1 to 8 to provide a clock frequency in the requested input range'.

Also all other PLL parameters are described to be dividers.

How do you get 80 MHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-04 11:36 AM

PLL is a high frequency oscillator conditioned by comparing its divided output to a reference clock.

You may want to look it up in some basic reference.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-04 11:52 AM

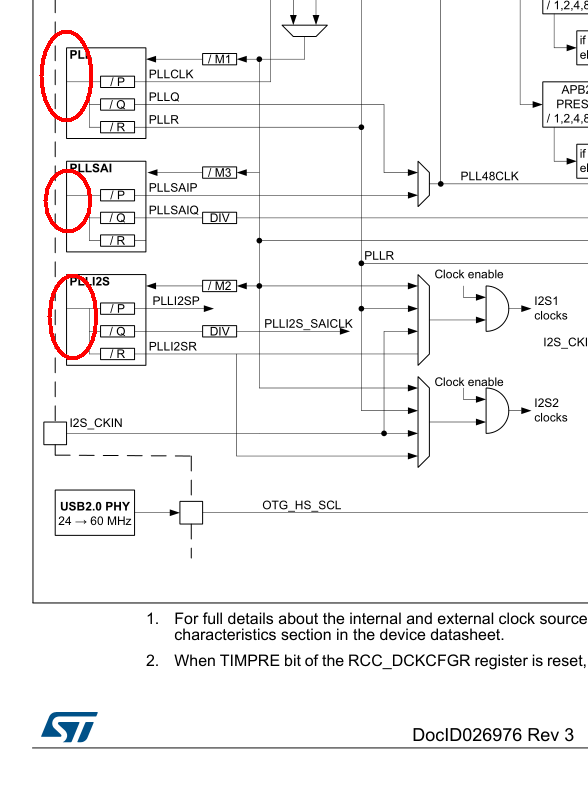

Ah, there's 'N' that's the multiplier. It was just not shown in the clock trees...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-04 02:54 PM

Hi,

http://www.st.com/en/development-tools/stm32cubemx.html

will help you to better understand the clocks and PLL configuration and will help you in configuring the clock tree.You'll achieve a 80MHz configuration with the following settings:

- HSE 8MHz PLLM=1, N=20, R=2

- or MSI 4MHz, PLLM=1, N=40, R=2

- ...

Regards

Bruno

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-05 02:49 AM

Hi Bruno,

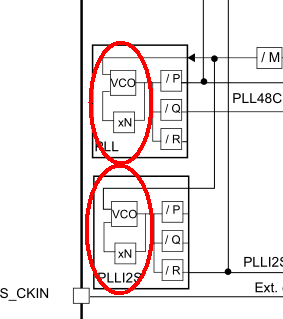

the block schematics in the RMs are perfectly understandable, except that those in the L4 RM miss the PLL ''multiplication'' element itself.

That was what turbo was talking about initially (and I misunderstood his question).

Please, re-instate the ''xN'' (even if the multiplication sign is factully incorrect there), as is in other families' RM (e.g. in RM0090):

Thanks,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-05 12:36 PM

Exactly, Jan. Thanks. Now that makes sense.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-05 02:09 PM

It's missing in RM0390 ('F446) too

ST, please, correct these RMs.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-07 02:13 AM

Hi,

You are right!

Thank you for bringing this issue to our attention.It is noted and will be fixed in coming release of the documents

-Nesrine-

- STM32 Open-Bootloader memory addresses in STM32 MCUs Embedded software

- A Question regarding DMA controller trigger source in STM32 MCUs products

- Flash Manager Module in STM32 MCUs products

- Wrong default linker FLASH STM32L412 in STM32CubeMX (MCUs)

- STM32L452CE CubeIDE Linker script causes hardfault inside Reset_Handler in STM32CubeIDE (MCUs)