- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- stm32R7VI widebus

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

stm32R7VI widebus

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-24 02:29 AM

I met an interesting problem. When I tried to configure this IO with SD widebus config (4bit) with hal libraries I always failed with initialization because pin 1 of SD card is on logic 0.

The solution was firstly let it initialize with pin 1 of SD card as GPIO with logic high as sdmmc core has logic 0 on this pin if it is configured as alternate function and before widebus initialization switch to alternate function.

So it is bug or feature of 4bit mode?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-24 07:09 AM

STM32R7VI ??

The code examples for the L4+ parts supporting SDMMC at 4-bit should be viable if correctly wired and no other board level pin conflicts. Code definitely workable on NUCLEO-64 and NUCLEO-144 boards, so look for bugs in your own design/implementation.

The STM32L4R9I-DISCO should work out of the box with provided examples.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-28 11:23 AM

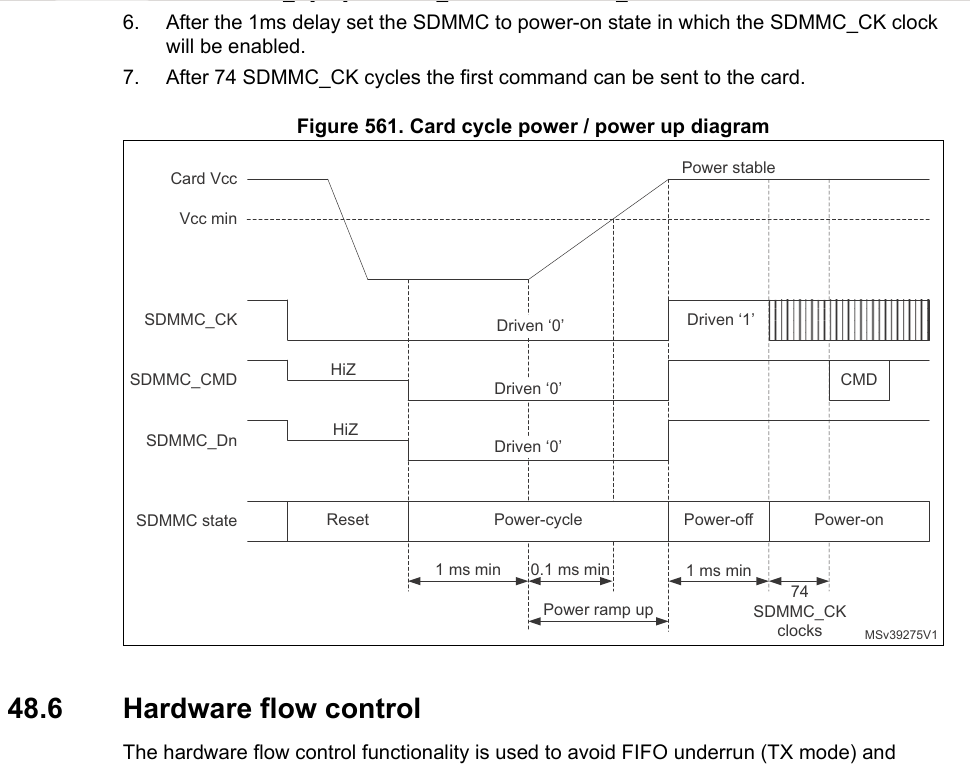

I quite studied manual for MCU and specification of SD cards. In sd specification and they recommend pull-ups for pins D0-D3 and CMD pin. However when I look on power-up sequence (page 1670 of reference manual) of SDMMC peripheral, there is something strange I think. Why sets the peripheral all these pins to logic '0' instead of let them hi-z until power stable (and let the pullups do the work) ?

Does the SDMMC peripheal expect that SD card ignores data on these pins during first 74 clock cycles?

This maybe work If you really do power sequencing. Question is if it will work if you have already card on power?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-28 01:53 PM

>>page 1670 of reference manual

Can we perhaps establish what part number you're working with, or what specific manual you're looking at? Provide a cite to product page or manual.

Clocking without a chip-select is usually part of clocking the device out of an unknown state, there isn't an async-reset pin here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-28 02:07 PM

point is that CS pin is asserted low when is logic 0 on D3 so it is active.

http://www.st.com/resource/en/reference_manual/dm00310109.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-28 02:40 PM

>>STM32R7VI

>>page 1670 of reference manual

Page 1760 of RM0432 Rev 1

Given the level of dyslexia here can you provide a schematic of what you've actually wired up?

The STM32L4R9I-DISCO board has a microSD card that works in 4-bit mode without any GPIO level meddling.

Diagram shows D3(CS) being high during the 74 clock sequence. State machine in card is supposed to recognize this.

>>Why sets the peripheral all these pins to logic '0' instead of let them hi-z until power stable (and let the pullups do the work) ?

Presumably to provide an effective route to ground and avoid corrupting/glitching the card? And not some indeterminate ramping voltage.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-08 08:22 AM

Ok. I was wrong with power sequencing. It is OK, card responses to command 8 normally. I also noted that mcu sends CMD55 two times. I edited a stm32l4xx_hal_sd.c file and removed double sending of CMD 55 in code and now initialization sequence works OK.

- SDMMC: How to recover from a TXUNDERR error, and live to write again in STM32 MCUs products

- Hello. Can you give me please a sample project with fatfs and sdio for TrueStudio? in Other tools (MCUs)

- Writing data from FSMC-connected SRAM to SD-Card via DMA in STM32 MCUs products

- SDIO Widebus operation failure in STM32 MCUs products