- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- stm32f2xx DMA re-enabling issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

stm32f2xx DMA re-enabling issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-01 03:25 AM

Hi,

I'm struggling with the DMA stream reenabling. I'm using 6 DMA streams to transfer known amount of data from memory to periph. Streams are triggerd with two PWM timers in the master-slave mode (update and CC trigers).

When transfer starts for the first time, everything works fine, but for each subsequent transfer I receive FIFO error interrupt flag, although DMA is configured in direct mode.

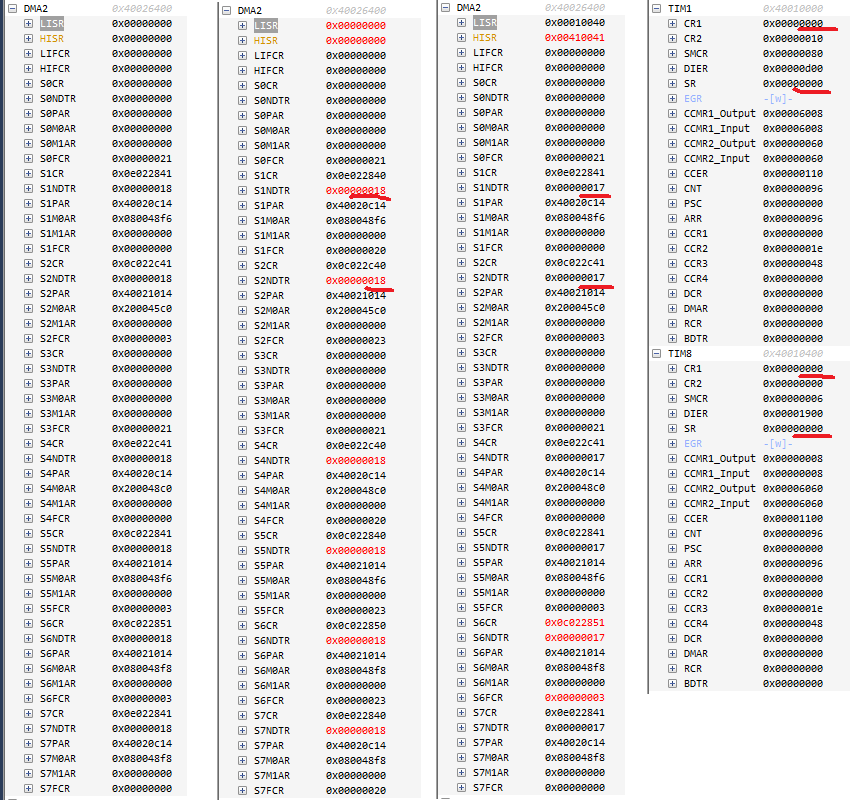

Pictures from the left side:

1. Before the first DMA transfer

2. After first (successful) transfer, all relevant DMA flags cleared and data counter set again

3. I

mmediately after DMA_Cmd(DMA2_StreamX, ENABLE); for every stream

4. Timers before (and after) enabling dma stream for the second transfer

Please notice that NDTR has been decremented for 1 (only 1) i

mmediately after enabling DMA stream although timers are disabled and all flags cleared, therefor there should be no triggering.

After enabling timers the rest 17 half-words are transferred correctly...

Can someone help me with this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-01 03:55 AM

I receive FIFO error interrupt flag, although DMA is configured in direct mode

In direct mode, you can simply ignore it.

Otherwise, you would need to disable the trigger source (here: timer through respective DIER bit) and reenable it after reenabling the DMA. There is a thread here from maybe a year or two ago explaining this behaviour but I am not going to search for it now.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-01 05:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-01 05:49 AM

Unfortunately I can't ignore it because I loose one transfer, as I've tried to emphasize in the previous post.

Never the less than you for the help, your hint for the DIER helped me.

Although DMA is in the direct mode, for some reason you must disable the trigger source and re-enable it after enabling the DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-01 06:15 AM

The reason is that DMA is level-triggered, and the trigger latch to catch the 'volatile' TIM events is not part of DMA but part of TIM.

Before I learned the trick with DIER, I worked around the same problem by forcing a trigger through respective bit in TIMx_EGR and then ignoring the result of first DMA transfer. This won't work well with M->P transfers I admit, I had the other direction.

JW

- Register-level examples for "more complex" interfaces, e.g. USB in STM32 MCUs Embedded software

- ADC overrun error. Multiple DMA usage. in STM32 MCUs products

- F4 DMA2 errata - how to handle that in STM32 MCUs products

- STM32F4 trouble with data transfer after USB reconnection with Android accessory ADK in STM32 MCUs products