Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Using advanced TIMs on STM32F746 Discovery for int...

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Using advanced TIMs on STM32F746 Discovery for interleaved converter

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-03 01:14 AM

Posted on March 03, 2016 at 10:14 The setup of the timers and the PWM channels are: TIM8CH1: Combined PWM2 TIM8CH2: PWM1 TIM8CH3N: PWM1 (TIM_OCNPOLARITY_HIGH) TIM8CH4: PWM1 TIM1CH1: Combined PWM2 TIM1CH2: PWM1 TIM1CH3: Combined PWM2 TIM1CH4: PWM1 TIM4: Master, trigger: TIM_TRGO_UPDATE TIM1, TIM8: Slave The register setup to output the correct timings is: TIM1->CCR1 = tim1ch1delay; TIM1->CCR2 = tim1ch1pulse; TIM1->CCR3 = tim1ch3delay; TIM1->CCR4 = tim1ch3pulse; TIM8->CCR1 = tim8ch1delay; TIM8->CCR2 = tim8ch1pulse; TIM8->CCR4 = tim8ch4pulse; TIM4->ARR = Period; TIM1 and TIM8 ARRs are set to 65535 to not interfere.

The setup of the timers and the PWM channels are: TIM8CH1: Combined PWM2 TIM8CH2: PWM1 TIM8CH3N: PWM1 (TIM_OCNPOLARITY_HIGH) TIM8CH4: PWM1 TIM1CH1: Combined PWM2 TIM1CH2: PWM1 TIM1CH3: Combined PWM2 TIM1CH4: PWM1 TIM4: Master, trigger: TIM_TRGO_UPDATE TIM1, TIM8: Slave The register setup to output the correct timings is: TIM1->CCR1 = tim1ch1delay; TIM1->CCR2 = tim1ch1pulse; TIM1->CCR3 = tim1ch3delay; TIM1->CCR4 = tim1ch3pulse; TIM8->CCR1 = tim8ch1delay; TIM8->CCR2 = tim8ch1pulse; TIM8->CCR4 = tim8ch4pulse; TIM4->ARR = Period; TIM1 and TIM8 ARRs are set to 65535 to not interfere. All works well on my scenario until a high duty cycle of the most shifted channel (i.e. TIM1CH3N in the following figure) overlaps with the first channel which is TIM8CH4.

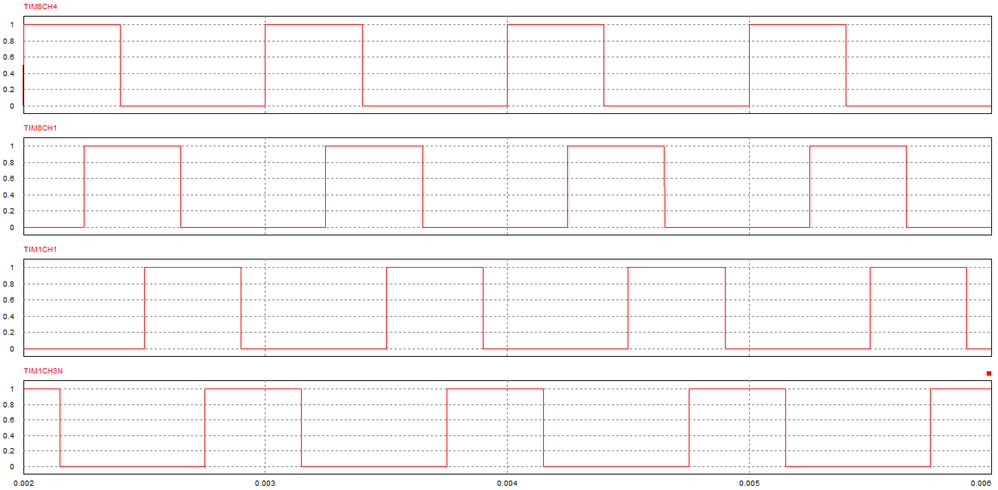

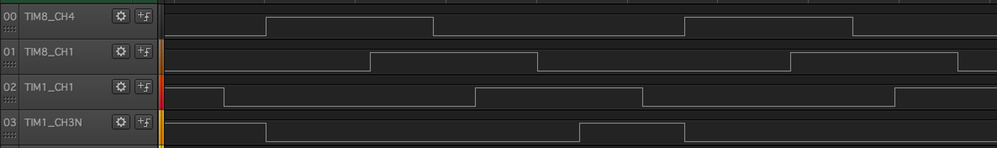

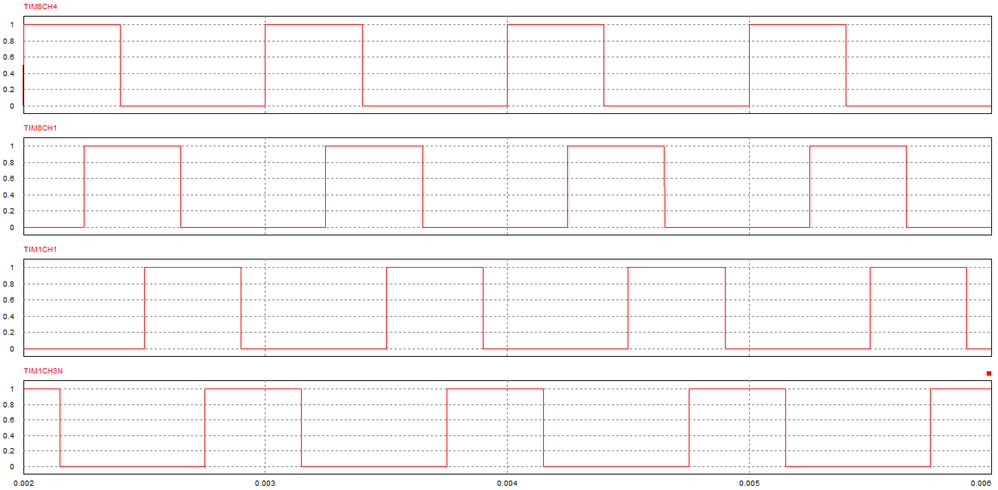

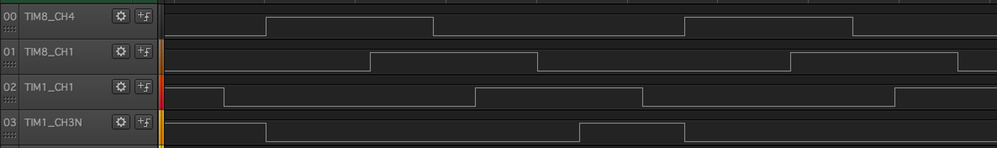

All works well on my scenario until a high duty cycle of the most shifted channel (i.e. TIM1CH3N in the following figure) overlaps with the first channel which is TIM8CH4.

As all of the timers reset at t=0.004, the output of TIM1CH3N will turn low. As this is the first time I have used the advanced features of the timers, I�d like to ask if someone thinks of a better implementation in order to overcome this problem for overlapping pulses. #advanced-timers #stm32f746discovery

As all of the timers reset at t=0.004, the output of TIM1CH3N will turn low. As this is the first time I have used the advanced features of the timers, I�d like to ask if someone thinks of a better implementation in order to overcome this problem for overlapping pulses. #advanced-timers #stm32f746discovery

Hello,

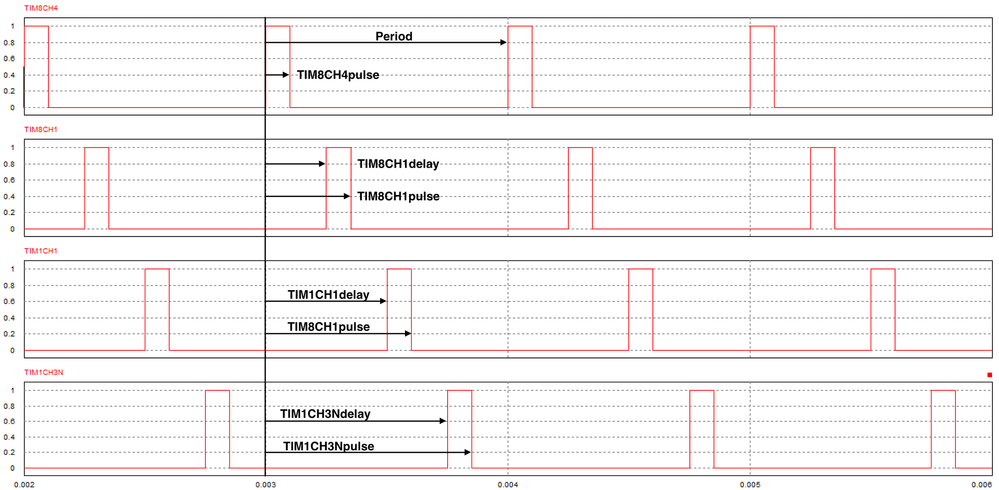

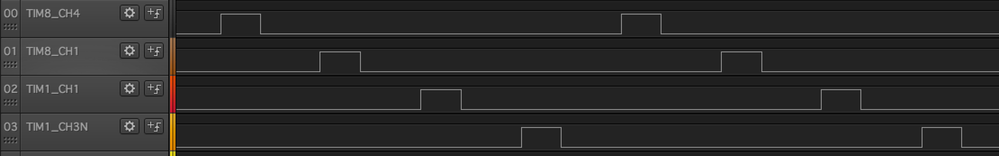

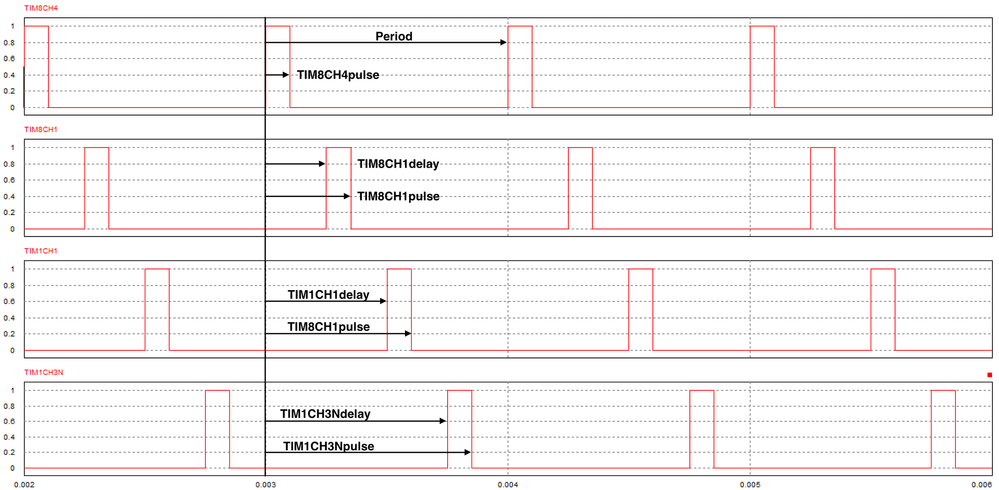

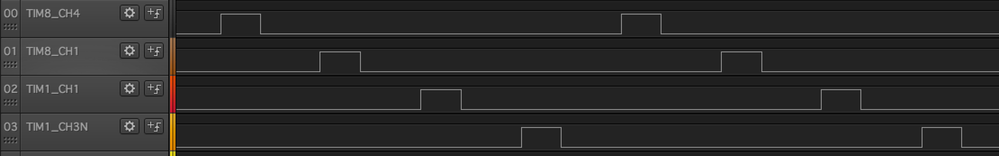

I have been designing a controller for an interleaved power converter using the STM32F746 Discovery board. Since I need to have four pulses with different duty cycles and phase delays (which will be variable), I have chosen to use both advanced control timers TIM1 and TIM8 in combined PWM mode. All of the pulses will have the same frequency which however will not be constant. To synchronize the two timers I have am using the third timer TIM4. So, the outputs of the four pulses are shown in the following figure. The setup of the timers and the PWM channels are: TIM8CH1: Combined PWM2 TIM8CH2: PWM1 TIM8CH3N: PWM1 (TIM_OCNPOLARITY_HIGH) TIM8CH4: PWM1 TIM1CH1: Combined PWM2 TIM1CH2: PWM1 TIM1CH3: Combined PWM2 TIM1CH4: PWM1 TIM4: Master, trigger: TIM_TRGO_UPDATE TIM1, TIM8: Slave The register setup to output the correct timings is: TIM1->CCR1 = tim1ch1delay; TIM1->CCR2 = tim1ch1pulse; TIM1->CCR3 = tim1ch3delay; TIM1->CCR4 = tim1ch3pulse; TIM8->CCR1 = tim8ch1delay; TIM8->CCR2 = tim8ch1pulse; TIM8->CCR4 = tim8ch4pulse; TIM4->ARR = Period; TIM1 and TIM8 ARRs are set to 65535 to not interfere.

The setup of the timers and the PWM channels are: TIM8CH1: Combined PWM2 TIM8CH2: PWM1 TIM8CH3N: PWM1 (TIM_OCNPOLARITY_HIGH) TIM8CH4: PWM1 TIM1CH1: Combined PWM2 TIM1CH2: PWM1 TIM1CH3: Combined PWM2 TIM1CH4: PWM1 TIM4: Master, trigger: TIM_TRGO_UPDATE TIM1, TIM8: Slave The register setup to output the correct timings is: TIM1->CCR1 = tim1ch1delay; TIM1->CCR2 = tim1ch1pulse; TIM1->CCR3 = tim1ch3delay; TIM1->CCR4 = tim1ch3pulse; TIM8->CCR1 = tim8ch1delay; TIM8->CCR2 = tim8ch1pulse; TIM8->CCR4 = tim8ch4pulse; TIM4->ARR = Period; TIM1 and TIM8 ARRs are set to 65535 to not interfere. All works well on my scenario until a high duty cycle of the most shifted channel (i.e. TIM1CH3N in the following figure) overlaps with the first channel which is TIM8CH4.

All works well on my scenario until a high duty cycle of the most shifted channel (i.e. TIM1CH3N in the following figure) overlaps with the first channel which is TIM8CH4.

As all of the timers reset at t=0.004, the output of TIM1CH3N will turn low. As this is the first time I have used the advanced features of the timers, I�d like to ask if someone thinks of a better implementation in order to overcome this problem for overlapping pulses. #advanced-timers #stm32f746discovery

As all of the timers reset at t=0.004, the output of TIM1CH3N will turn low. As this is the first time I have used the advanced features of the timers, I�d like to ask if someone thinks of a better implementation in order to overcome this problem for overlapping pulses. #advanced-timers #stm32f746discovery

Labels:

- Labels:

-

STM32F7 Series

-

TIM

0 REPLIES 0

Related Content

- STM32G474 discovery kit no voltage at Vin in STM32 MCUs Boards and hardware tools

- STM32F411 ADC full capacity with USB in STM32 MCUs products

- STM32G474 FMAC for 3p3z controller in STM32 MCUs Embedded software

- STM32F407VG ADC DMA Interleaved Mode in STM32 MCUs products

- Issue with multichannel ADC readings in stm32f334r8 in STM32CubeIDE (MCUs)