- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- How to obtain the maximum USB-Transfer-Speed of ST...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to obtain the maximum USB-Transfer-Speed of STM32F4 with ULPI in Device-Mode [solved]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-08-26 10:39 AM

Hardware / Configuration:

STM32F407vgt6 @168MHz USB3300 ULPI (waveshare) @24MHz USB HS + DMA Bulk Transfer (IN-Transfer) Modified cdc-Example (STM32_USB-Host-Device_Lib_V2.1.0) libusb-1.0.19-10903 Hello , I try to obtain the maximum Transfer-Speed for the STM32 in Device-Mode. I Try to Transfer 15MiB from Device to Host over libusb as fast as possibile. Every time a ''DataInComplete'' occures, I start another 512-Byte ''DCD_EP_Tx()''-Transfer of generated Data. My Problem is, that my logic-Analyzer detect every 3 Transfers a Error, probaly because the Data is not complete prebuffered. What could be the Problem / What could I try ? #stm32-ulpi-usb-hs-bulk-libusb #usb #fifo #device

#stm32-ulpi-usb-hs-bulk-libusb #usb #fifo #device

- Labels:

-

USB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-08-28 09:19 PM

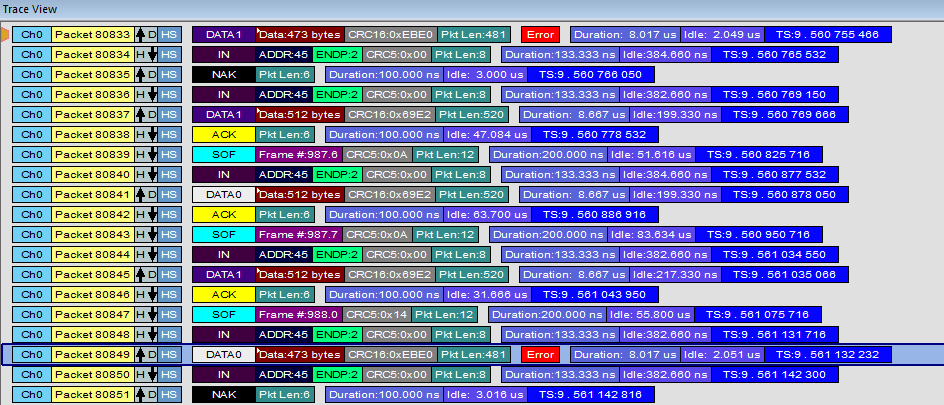

In your trace, two problems are seen,

1) transaction error 2) NAK appears too often1) transaction error

> My Problem is, that my logic-Analyzer detect every 3 Transfers a Error,Maybe, it's a problem of endpoint FIFO allocation?

Recommended FIFO allocation is,usb_conf.h

line:119

/****************** USB OTG HS CONFIGURATION **********************************/

#ifdef USB_OTG_HS_CORE

#define RX_FIFO_HS_SIZE 384 // (in DWORD = 1536 bytes)

#define TX0_FIFO_HS_SIZE 32 // (in DWORD = 128 bytes)

#define TX1_FIFO_HS_SIZE 16 // (in DWORD = 64 bytes)

#define TX2_FIFO_HS_SIZE 512 // (in DWORD = 2048 bytes)

#define TX3_FIFO_HS_SIZE 0

#define TX4_FIFO_HS_SIZE 0

#define TX5_FIFO_HS_SIZE 0

// total 934, 90 DWORD is reserved> Every time a ''DataInComplete'' occures, I start another 512-Byte ''DCD_EP_Tx()''

You may pass transfer size greater than 512 (one packet) to DCD_EP_Tx(). For example, 4K bytes or more, as much as your data RAM size allows. In this way, you can reduce the NAK ''gap'' between the transactions.

3) RM descriptionThe decision of endpoint FIFO size is complicated.

- While DMA is applied, the USB core reserves one DWORD per each TX endpoint at the end of FIFO - TX0_FIFO_HS_SIZE requires at least 32 DWORD Unfortunately, the OTG_FS/OTG_HS sections of STM32 Reference manuals don't describe it fully.SiLabs (Energy Micro) EFM32 family has almost the same USB IP as STM32F4/L4/F7, provided by Synopsys. Around 85% of USB description on the reference manuals is common in word by word, but the EFM32 description is much revised from STM32's. Compare ''FIFO RAM Allocation'' section of STM32 withEFM32's,

, 10 FIFO RAM allocation (p1396)http://www.silabs.com/Support%20Documents/TechnicalDocs/EFM32WG-RM.pdf

, 4.7 FIFO RAM Allocation (p329) ST should claim revised USB IP description for the RM's to Synopsys, at least those they had provided to SiLabs (in 2014-07-02).Tsuneo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-08-29 01:18 AM

- Stm32F4O7VET6 Custom board Vcap1 and Vcap2 problem in STM32 MCUs Boards and hardware tools

- Configuring ITM on STM32U5 in STM32 MCUs Embedded software

- Trying to adapt stm32f4 for stm32l452RE in STM32 MCUs Embedded software

- STM32F4 OSC Problem in STM32 MCUs products

- STM32F4 bricks sometimes in STM32 MCUs products