- STMicroelectronics Community

- Product forums

- STM8 MCUs

- External interrupt flags latching behaviour?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

External interrupt flags latching behaviour?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-10 01:46 AM

I am working on a code which utilizes External interrupts on the PORT B.

STM8AF5286 is used with the Cosmic compiler.

I have not found any information about how the interrupt flags are handled internally and knowing their behavior would be important for my project.

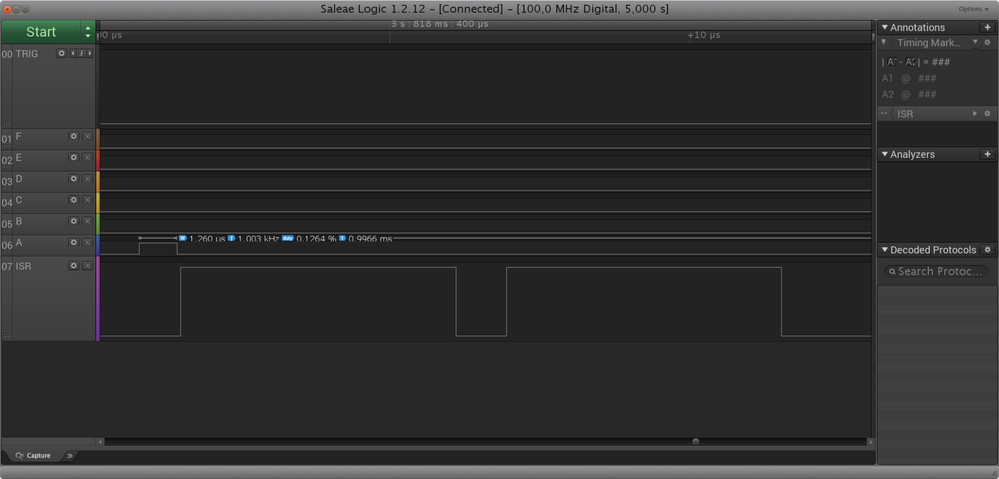

On the logic analyzer capture below you can see that the pulse on the PORTB 0 is 1.26 us, which triggers two interrupts. which first and last instruction toggles the pin captured with the ISR channel.

The PB_ODR read is performed in the next instruction after the ISR pin low to high transition.

In both routines it reads zero from the PORT B.

Is there any way to clear the pending interrupt flag in the serviced interrupt routine?

#external-interrupt #interrupts- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-25 01:27 PM

I got a similar problem. I noticed that when there is a transition of an external interrupt pin while in the interrupt routine servicing this interrupt, immediately after you finish the interrupt routine it will fire another one. The only way to avoid this is to immediately disable EXTI interrupt on that particular pin inside the interrupt service routine.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-08 03:33 AM

This occurs due sensitivity selection parameter configuration for external interrupts. Most of stm8 micro controllers provide the following options

00: Falling edge and low level

01: Rising edge only10: Falling edge only11: Rising and falling edgeThe default being 00 you might be seeing a repeated ISR's if you are not configuring the sensitivity to a value different than 00 (based on the application).

- LIS2DW12 latching INT1 pin to GND on board reboot in MEMS (sensors)

- inconsistent behaviour in TIMER and CCxR interrupt in STM32 MCUs products

- STM32G491 FDCAN: Issue with error counters in STM32 MCUs products

- Debug ST-Link MINIE using the ADC , GP DMA and TIM strange behaviour in STM32 MCUs products

- UART CTS signal stuck at high after framing error in STM32 MCUs products