- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- ['F446 documentation] SAI/SPDIF-Tx bit clock formu...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

['F446 documentation] SAI/SPDIF-Tx bit clock formula missing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-16 03:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-16 03:47 AM

On second thought - I've seen the formula in other RMs, but IMO that formula ought to be given in terms of SAI signals as defined and SAI registers fields (namely MCLK), as it's different than clocking in free protocol modes (in that FRL is ignored).

The formula at MCLK's description ought to say so, too.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-24 11:43 AM

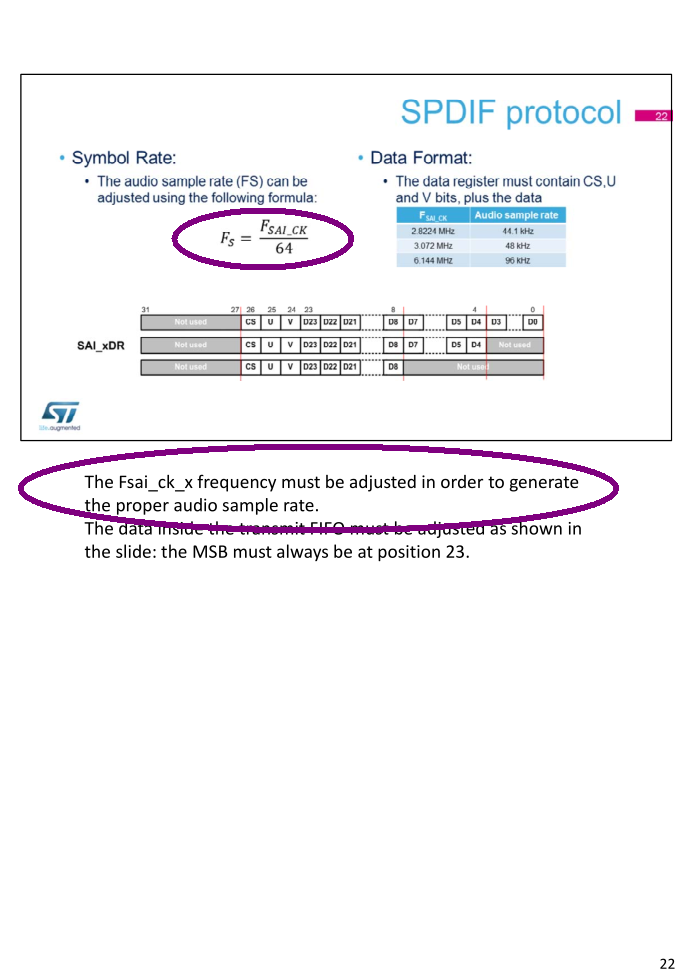

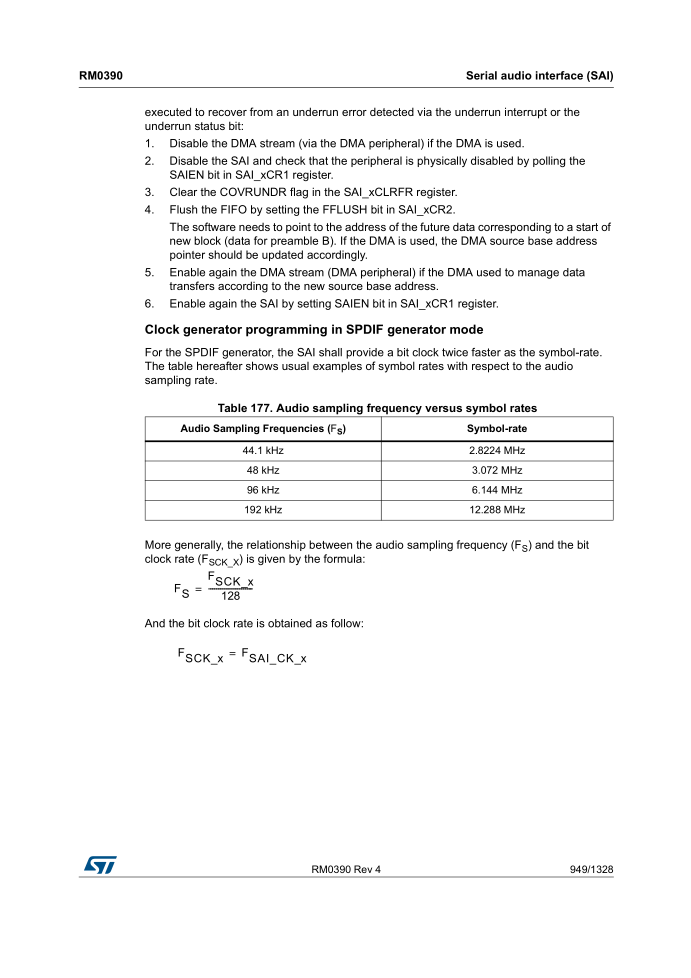

The formula I mentioned above I've seen in 'F7 documentation is wrong anyway:

as fS is not fSCK_x/64; and certainly not fSAI_CK_x / 64.

And this is wrong, too:

as it's not just the input frequency to SAI block, i.e. fSAI_CK_x , which is alone responsible for the resulting sampling frequency.

The fact is that (denoting the SPDIF symbol rate fSYMB) fS = fSYMB / 64; but fSYMB=fSCK_x / 2.

And, fSCK_x follows the same rules as in FREE mode, i.e. fSCK_x = fSAI_CK_x if NODIV=1; fSCK_x = fSAI_CK_x / (256 / (FRL+1)) if NODIV=

1

0[EDIT]was a typo, sorry[/EDIT]

and MCKDIV=0; and fSCK_x = fSAI_CK_x / ((2 * MCKDIV) * 256 / (FRL+1)) otherwise; where (FRL+1) = 64.In other words, the final fS-to-fSAI_SCK_x ratio is half of what would be for the FREE mode with the same NODIV and MCKDIV settings.

Of course, Cube gets it wrong, too; as it does not account for this factor of half. The only example I could find for SAI in SPDIF-Tx mode (namely in [STM32Cube_FW_F7_V1.7.0]\Projects\STM32F769I-Discovery\Examples\SPDIFRX\SPDIFRX_Loopback\) has no visible/audible output, and uses as receiver the SPDIFRX module, which is adaptive enough to ignore the fact that the output sample rate is half of what was intended.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-05 05:41 AM

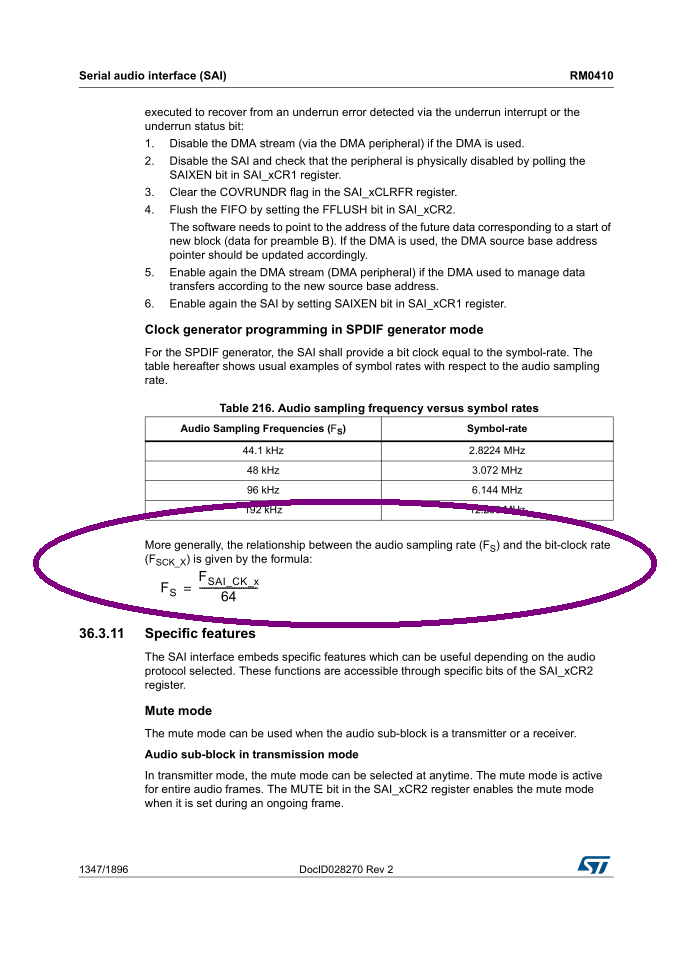

While in the new RM, the formula is there:

it's only partially true. As I've said above, fSCK_x follows the same formula as in FREE mode, with that the setting in FRL is ignored and is taken as if is fixed (FRL+1)=64.

Thus:

if NODIV=1 fSCK_x = fSAI_CK_x

If NODIV=0 and MCKDIV=0, fSCK_x = fSAI_CK_x / 4

If NODIV=0 and MCKDIV>0, fSCK_x = fSAI_CK_x / (8 * MCKDIV)

JW

- WIFI module in STM32 MCUs Boards and hardware tools

- Missing CMOX_AESFAST_CFB_DEC_ALGO in STM32 MCUs Security

- MMT not available in tools menu in STM32CubeIDE (MCUs)

- can this article be used to write external loader OSPI for Keil? in STM32 MCUs products

- STM32U5 series bank swap not working in STM32 MCUs Embedded software