Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- I2S (in SPI): I2SDIV [7:0] = 1

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I2S (in SPI): I2SDIV [7:0] = 1

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-22 01:57 AM

Posted on January 22, 2018 at 10:57 null

null

In RMs for 'F4/'F7/'F0 (I didn't check further), in SPIx_I2S prescaler register (SPIx_I2SPR) chapter, I2SDIV description, the following statement is given:

I2SDIV [7:0] = 0 or I2SDIV [7:0] = 1 are forbidden values.

However, I've experimented with I2SDIV [7:0] = 1 back then - described in

https://community.st.com/0D50X00009XkYmHSAV

,I can't access it due to broken forum software

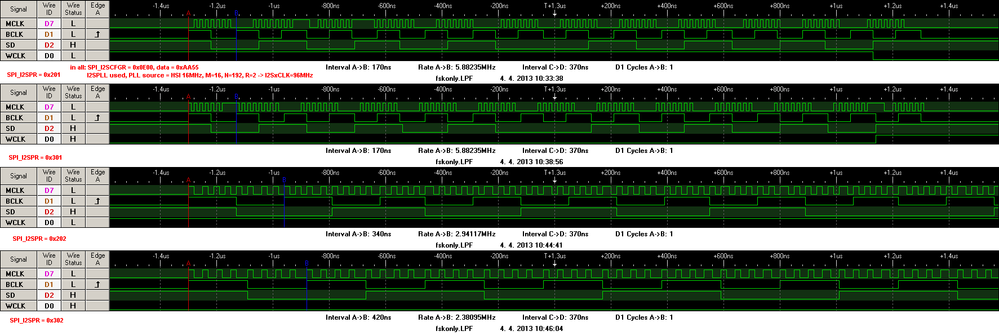

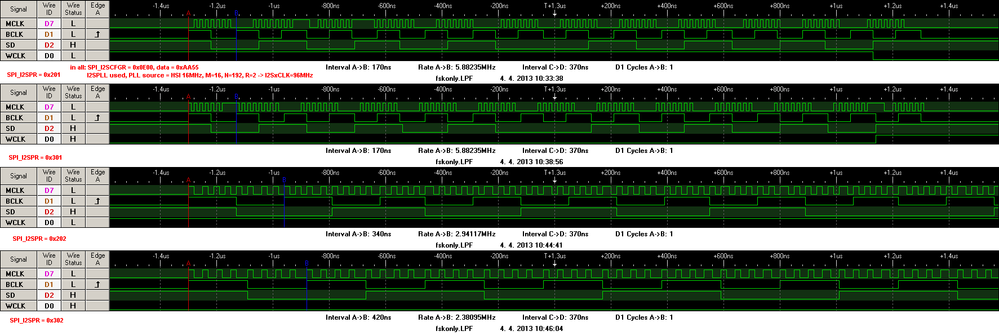

, original attachment shown below (MCLK in first two cases shown discontinuous as I chose inadequate sampling rate on LA... blushing... ). Results show, that I2SDIV [7:0] = 1 works as expected (dividing input clock by 2) as long as ODD = 0.It is beneficial to have as low divider for I2S as possible, as it lowers requirement for input clock (thus consumption and EMI).

Can please ST review this description and, if there's no other catch, allow I2SDIV[7:0]=1 provided that ODD = 0?

Thanks,

Jan Waclawek

null

null

0 REPLIES 0

Related Content

- STM32H573 I2S audio clock problem in STM32 MCUs products

- stm32f407 - Question of i2s clock frequency in STM32 MCUs products

- I2S Clock vs Sampling Frequency(Fs) for sampling MP45DT02 on STM32F4 Discovery in STM32 MCUs products

- Can ST please review the requirement of I2SDIV > 2 in SPI/I2S of 'F2/'F4? in STM32 MCUs products