- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- [OTG + documentation] miscellanous typos, omission...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[OTG + documentation] miscellanous typos, omissions, clarification needs, etc.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-23 01:08 PM

I have more such questions/remarks on the OTG IP module. I am tired of waiting here, so started to add them in the ever-growing '

http://www.efton.sk/STM32/STM32F4xx_doc_errors.txt

' document I write on the STM32F4xx.JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-29 12:15 PM

OTG-related extract:

STM32F405xx and STM32F407xx Datasheet DocID022152 Rev 8 September 2016

Tab9 Alternate function mapping

- throughout the whole table, column AF12 is marked 'FSMC/SDIO/OTG_FS'. There is no OTG_FS function in AF12, but there are OTG_HS functions. This column should be thus labeled 'FSMC/SDIO/OTG_HS'.p128 and on - USB OTG FS characteristics - 'This interface is present in both the USB OTG HS and USB OTG FS controllers.' - both the title and this line is confusing. This chapter does not deal with particularities of the OTG_FS module, but deals with the characteristics of the FS_PHY, which is built together with both the OTG_FS and OTG_HS modules. Please use the word 'PHY' to make this clear and on par with RM0090 rev.15 '3.2 Full-speed OTG PHY' and '3.3 Embedded Full-speed OTG PHY'.

p130 - in Table , no values are given for 'PHY preparation time after the first transition of the input clock'

RM0090 rev 15

p372 - in 'OTG_FS WKUP' acronym, an underscore is missing - it would be nice to add to its description, that it's EXTI 18 (I know it's on p.383 but this table should contain it too) - there is no explanation in this or the OTG_FS chapter, how is this interrupt configured and triggered p379 - it would be nice to add to OTG_HS_WKUP description, that it's EXTI 20 (I know it's on p.383 but this table should contain it too) - there is no explanation in this or the OTG_HS chapter, how is OTG_HS_WKUP interrupt configured and triggered. The text on p.383 'EXTI line 20 is connected to the USB OTG HS (configured in FS) Wakeup event' is even more confusing; I could find no mention in the OTG_FS chapter for this configuration either. Is this again supposed to say 'FS_PHY connected to the OTG_HS module'? There is no dedicated FS_PHY_in_OTG_HS text which would mention this interrupt, either. - there is no explanation in this or the OTG_HS chapter, how are OTG_HS_EP1_IN and OTG_HS_EP1_OUT interrupts configured and triggered. .both OTG chapters - textual search for 'OTG_HS' finds one instance in the OTG_FS chapter; and for 'OTG_FS' finds about half a dozen of them in the OTG_HS chapter p1260+p1295 - chapter '9 Dynamic update of the OTG_FS_HFIR register' explicitly allows changing OTG_FS_HFIR while the module is operating, while description of the only field in this register (FRIVL) contains ' Do not change the value of this field after the initial configuration.' - this is a contradiction p1273+p1326 - reset value of OTG_FS_GOTGCTL is given in the register's description as 0x00000800, in the table reset value of the reserved bits are not given but all other bits are given as 0 except CIDSTS which is given as 1, which assuming all reserved bits at 0 would yield 0x00010000; while in a rev.Z STM32F407 it is found to be 0x00100000. The same applies for OTG_HS_GOTGCTL. p1274+p1406 - the narrative for OTG_FS/HS_GOTGCTL.SRQ bit says 'This discharge time varies between different PHYs and can be obtained from the PHY vendor.'. Isn't ST the PHY vendor in this case? Please clarify. p1285+p1419 - OTG_FS_GINTMSK/OTG_HS_GINTMSK contain EPMISM bit as bit 17, according to description to enable 'Endpoint mismatch interrupt'; there is no such interrupt described elsewhere and the respective bit 17 in OTG_FS_GINTSTS/OTG_HS_GINTSTS is marked as reserved. (There is a mention of endpoint mismatch around OTG_HS_GINTSTS.DATAFSUSP description; but I suspect this part of that narrative should not be there for the given configuration of this IP). p1291 - reset value of OTG_FS_GCCFG is given as 0x00000000, while in a rev.Z STM32F407 it is found to be 0x0000FFFF (btw. in the table at end of chapter, reset value of the reserved bits is not given at all; OTG_HS_GCCFG *is* 0x00000000 after reset as documented) p1292+p1327 - reset value of OTG_FS_CID is given at both those pages as 0x00001100, while in a rev.Z STM32F407 it is found to be 0x00001200 (btw. OTG_HS_CID *is* 0x00001100 after reset as documented) Also, the description says 'This is a read only register containing the Product ID.', while the bits are marked as 'rw' and experiment shows this is indeed a writable register. p1307 - OTG_FS_DIEPMSK.INEPNMM ought to mask 'IN token received with EP mismatch' interrupt, but the respective bit5 in OTG_FS_DIEPINTx is marked as reserved (cf. also above OTG_FS_GINTMSK.EPMISM). While in OTG_HS_DIEPINTx this bit is present, I suspect it still should not be there for the given configuration of this IP. p1308+p1320 - the respective bit6 to mask OTG_FS_DOEPINTx.B2BSTUP is in OTG_FS_DOEPMSK marked as reserved (in HS, both the B2BSTUP mask and interrupt bits are present) p1394 - figure 'SOF trigger output to TIM2 ITR1 connection' is unnumbered. There is also a clickable link to this figure on the same page, 'Figure' with no number. p1336+p1486 - in 'Device initialization' chapter in both OTG_FS and OTG_HS 'programming model' description, item 3. says '... and supply the 5 volts across the pull-up resistor on the DP line'. As the pullup is built-in into PHY, this should not be needed and is confusing, please remove. p1398+p1403+p1451-1453 - functionality of OTG_HS_DEACHHINT/OTG_HS_DEACHHINTMSK/OTG_HS_DIEPEACHMSK1/OTG_HS_DOEPEACHMSK1 is not explained. They are mentioned also in Fig. 412, but with no clear indication what endp_multi_proc_intrpt and endp_interrupt[31:0] signals are supposed to trigger.Note also the

https://community.st.com/thread/31122#comment-159345

.JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-14 02:36 AM

Hello Jan,

You have highlighted limitations and suggested improvements on the USB section of our reference manuals: An action was taken and the USB chapter was reworked: Mistakes corrections, new clarification added...

All the reference manuals which include a USB OTG chapter are updated and will be available on web.

Currenly, is available (with the needed updates), the others will follow on the coming days.We convey our sincere thanks to you for the feedback you have provided and we really appreciate your valuable contribution on our STM32 MCUs forum.

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-14 05:56 AM

Ah, nothing like a smell of a brand new RM! 😉

Thanks, Khouloud.

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-14 06:19 AM

You're always welcome

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-14 09:29 AM

Waclawek.Jan

Thanks for the comment. We wanted it, to be ourValentine's Day Gift

for you !

🙂

🙂

Cheers,

STOne-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-03 01:41 AM

Hi

garsi.khouloud

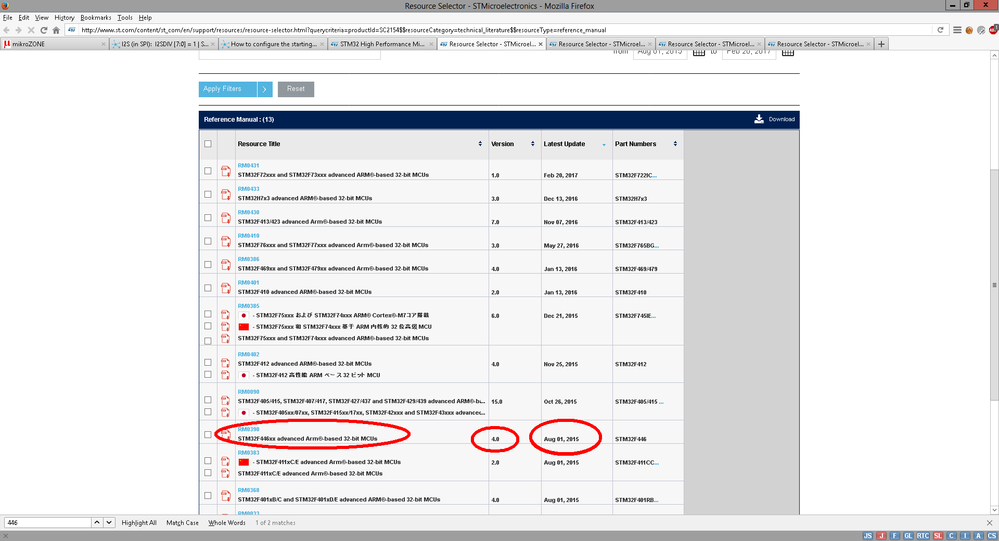

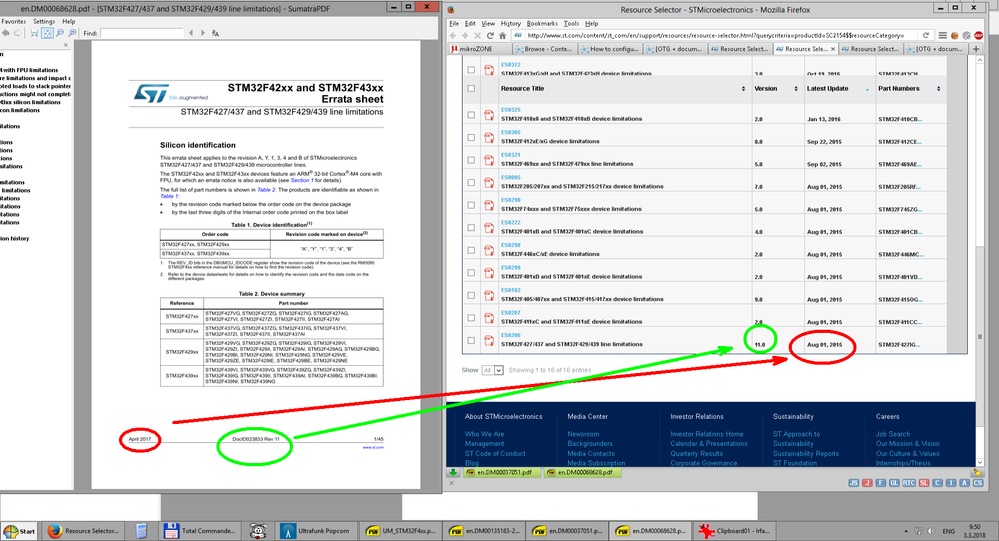

could the date of RM change also be updated in the Resources selector?

Thanks,

Jan

[EDIT] PS. This appears to be a more widespread problem...

https://community.st.com/0D50X00009XkaRZSAZ

[EDIT2] Yes it is... a random example, I checked half a dozen RM and DS and ES and *all* had incorrect date...

In the above linked thread I'll discuss the importance of maintaining this information properly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-05 03:33 AM

Hi Jan,

I have highlighted this internally. Sorry for any caused inconvenience.

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-24 11:33 AM

Hello Jan,

I have two good news

1. The

is updated and now available on ST website.In this discussion, two open points are still under discussion. Otherwise, all other issues were discussed and fixed, and the 'Interrupt hierarchy' figure was fully reworked.

2. The 'Latest update' column in the 'Resource Selector' is updated correctly now.We really thank you for highlighting all encountered issues through our Forum, this helps us to enhance the quality of our documents.

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-24 03:35 PM

Hi Khouloud,

Thanks for letting me know. This will take some time to digest... 🙂

I took a quick look though, and the

https://community.st.com/0D50X00009XkaCPSAZ

I checked was not fixed/hidden... 😉JW

- External Powering of NUCLEO-L031K6 HSI able to run? in STM32 MCUs Boards and hardware tools

- What's the value of efforts towards better documentation? in STM32 MCUs products

- Unable to get the Touch function running properly XPT2046 in STM32 MCUs TouchGFX and GUI

- STM32U575 Analog Watchdog with Oversampling on ADC1. Need clarification of the reference manual in STM32 MCUs products

- Switching from Debug to Release mode - how do I push firmware to target (beginner question, am I doing something wrong?) in STM32CubeIDE (MCUs)