- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32L476 SAI2 block B not working!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32L476 SAI2 block B not working!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-18 11:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-18 11:04 AM

Please notice that debug was OK

Codec is initiliased using the I2C good and then all callbacks was ok to start IT.Next day I can check signals with logic analyzer. But know it is late bacause it is a software bug (or feature) of current HAL libary with the latest MX for L series- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-19 02:44 AM

Also notice the block B on SAI1 is working! I created an another tests and shoose different pins from B block. Anything was ok.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-19 07:43 AM

Seems to be no answers. Then I created the support ticket and no answer too.

Too bad to understand how boring is the stm32 development.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-19 11:12 AM

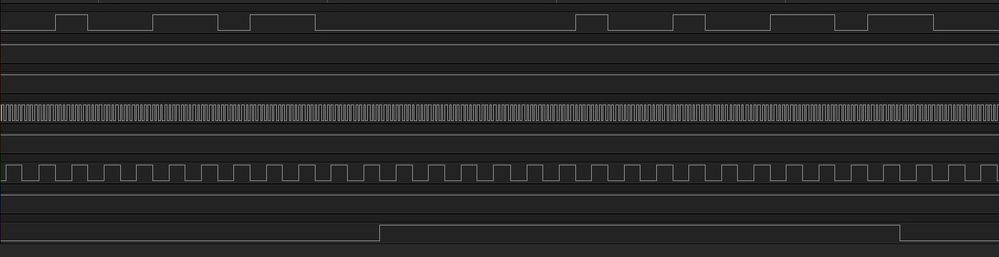

I attached 2 files.

In non working example with SAI2 you can see only MCLK and SCK.

Another signals seems to be no (logic one everwhere).

But in another picture with standard example everything is ok

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-19 11:24 PM

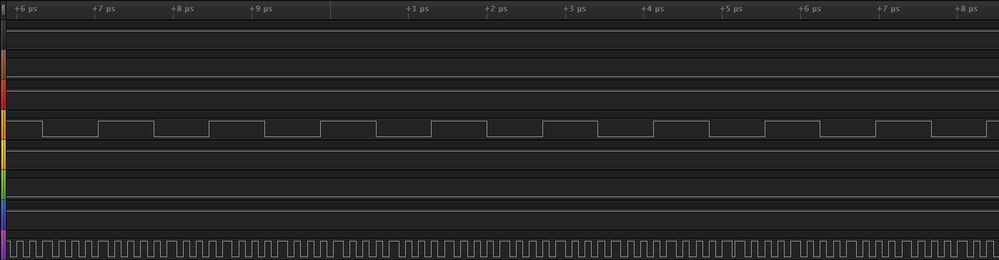

Logic one - for I2C and reset - this is normal

But other important lines are zero!- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-21 12:51 AM

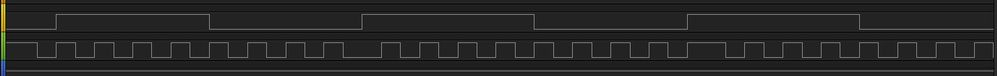

Sorry. In the first message I gave an incorrect info about block B of SAI1. It is not working too with the same thing described in picture! You can see only near 700KHz bit clock signal and 6 Mhz input clock signal for codec. Codec init was succes on I2C but then the same situation is here too.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-21 12:58 AM

For B block tests I redefine the definitions in example to SAI:

#define AUDIO_SAIx SAI1_Block_B#define AUDIO_SAIx_CLK_ENABLE() __HAL_RCC_SAI1_CLK_ENABLE()#define AUDIO_SAIx_FS_GPIO_PORT GPIOB#define AUDIO_SAIx_FS_AF GPIO_AF13_SAI1#define AUDIO_SAIx_FS_PIN GPIO_PIN_6#define AUDIO_SAIx_SCK_GPIO_PORT GPIOB#define AUDIO_SAIx_SCK_AF GPIO_AF13_SAI1#define AUDIO_SAIx_SCK_PIN GPIO_PIN_3#define AUDIO_SAIx_SD_GPIO_PORT GPIOB#define AUDIO_SAIx_SD_AF GPIO_AF13_SAI1#define AUDIO_SAIx_SD_PIN GPIO_PIN_5#define AUDIO_SAIx_MCLK_GPIO_PORT GPIOB#define AUDIO_SAIx_MCLK_AF GPIO_AF13_SAI1#define AUDIO_SAIx_MCLK_PIN GPIO_PIN_4 #define AUDIO_SAIx_MCLK_ENABLE() __HAL_RCC_GPIOB_CLK_ENABLE()#define AUDIO_SAIx_SCK_ENABLE() __HAL_RCC_GPIOB_CLK_ENABLE()#define AUDIO_SAIx_FS_ENABLE() __HAL_RCC_GPIOB_CLK_ENABLE()#define AUDIO_SAIx_SD_ENABLE() __HAL_RCC_GPIOB_CLK_ENABLE()- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-21 01:12 AM

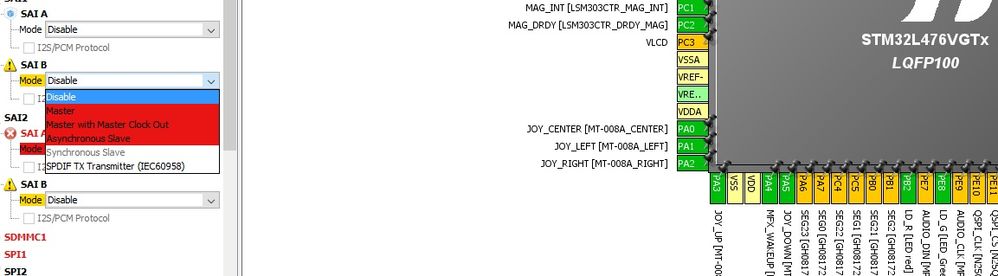

I also cann't understand why I cann't choose the block B in cubeMX software to choose the master mode with clock output?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-21 01:54 AM

- Problem With UDP Broadcast receive in STM32 MCUs products

- Help needed for tuning 64Mb HYPERRAM (S27KL0642DPBHI020) on STM32H735IGT6 in STM32 MCUs products

- STM32U5A5: PSRAM (4MB external RAM) via QSPI (OCTOSPI1) - for you in STM32 MCUs products

- Firmware Update in STM32CubeProgrammer (MCUs)

- Help with 90 degree rotation of image with MDMA linked-list in STM32 MCUs Embedded software