- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Best ADC conversion method and clamping?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Best ADC conversion method and clamping?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-13 06:33 PM

Hi Guys,

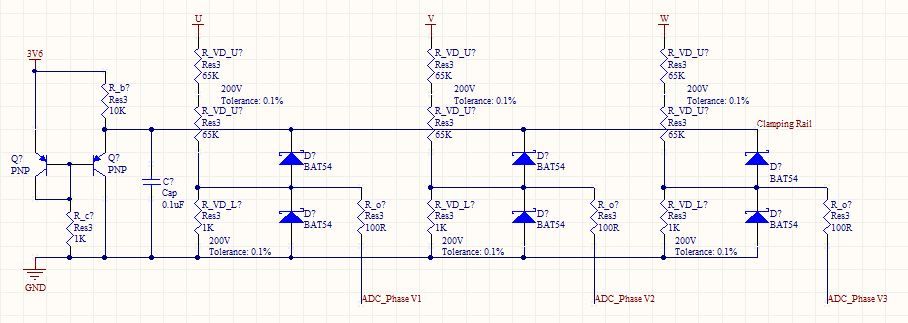

I'm designing a 3-phase DTC induction motor control which needs the 3-phase voltages and 2 of the currents. I am using the STM32F4 Discovery board. The control will have a small sample time (5uS). The controller may issue a new switch state every 5uS, and therefore the 5 ADC must take place every 5uS. Assuming due to the inductance of the motor the voltages/currents will need, lets say, 2.5uS to settle. Therefore i have only 2.5uS to do these 5 ADC's. The control loop is highly sensitive to these 5 parameters, therefore the more accurate the readings the better. Also, it is best to do these readings as close (in time) to each other as possible. I see this STM32 chip has many ADC setups, so what is the best method to go about this? Ideally it would be good to have a synchronized trigger just before my main control loop to read all the ADC values into DMA, then I can just read the values without interrupting the flow of the code. Is this going to be too hard to get them sampled within a reasonable time? Another alternative is to just use the DC bus voltage and switch states to estimate the 3-phase voltages. Although this is mathematically less accurate, perhaps just having 3 ADC conversions (DC bus voltage, and 2 currents) will end up a more accurate solution? Also, my UVW phase voltages will be 0~400V . I was thinking of scaling the voltages 130:1 (max 468V) and clamping using the following schematic. Thoughts? Im not sure what value i should use for R_o. Thanks for your help in advance! Stefan #clamping #dtc #adc-stm32-discovery #mcu #adc

Thanks for your help in advance! Stefan #clamping #dtc #adc-stm32-discovery #mcu #adc

- Labels:

-

ADC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-14 12:05 AM

The raw numbers of 2.4Msps as given in the datasheet are looking ok.

It is stated in the referenc manuals that the actual resolution, i.e. the accuracy, reduces with shorter conversion cycles. If this does not suffice, you could try a ping-pong mode, i.e. connect two ADC channels to each input, and convert in an overlapping mode. You will need to use DMA anyway, because each ADC has only one result register. One suggestion: Get some kind of function generator to emulate the input signal(s), and test your conversion concept and software with that.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-14 04:59 AM

Your scaling is 131:1.

Ro should be a unity gain operational amplifier to provide a low impedance input to the ADC. Otherwise, the sampling time would have to be too long to get an accurate conversion. If you go with just 3 inputs, triple simultaneous mode will provide the best performance. See the example for this mode provided with the standard peripheral library. For 5 inputs, consider triple simultaneous mode with two channels per ADC. Cheers, Hal- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-14 05:38 AM

Thanks for your reply, fm.

I'm still learning and not sure really what the difference is between injected and regular channel groups are. But injected has 4x16bit registers and regular 1x16 (total 5x16bit - perfect?). Perhaps I can set 4 of the conversions to injection and the remaining solo in the regular group, that would give 1x16bit register per conversion - Im not sure if this helps anything? Also, I'm new to the calcs, can someone look over these for me? If I used a sampling time of 3 cycles. Conversion time would be 3+12=15 clock cycles. APB2 is 84Mhz on the STM32F4, so that would equal 15*(1/84Mhz) = 0.18uS... I think.. Maybe that needs to be *2 looking at the calculation on RM0090 page 215. What does the ADCCLK effect? Just the sample clock cycles? I'm guessing each ADC channel has its own sample and hold cap, therefore can those 3 sample cycles be done in parallel for each of the 5 signals? i.e the above calculation then for sampling 3 signals (one in each ADC) would take the same time as just one? And then for 5 signal conversions (using 3 ADCs, and then 2 ADCs). The conversion time would be; (3+2*12)*(1/84M)=0.32uS? Since I am converting essentially a DC voltage (PWM either high or low) with a filter cap. If i give the signal enough time to settle either high or low, will 3 clock cycles be long enough? Also, its worth noting I added a buffer amplifier to each signal and got rid of R_o Thanks for your help- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-14 05:46 AM

Thanks Hal.

Yes I have already made the change to a unity opamp, I realised that mistake shortly after my first post. Will the triple simultaneous mode with 2 channels per ADC result in a conversion time as per my previous post? What prescale of ADCCLK should I use for my 200khz square wave? The shortest pulse will last 5uS, but I want to allow at least 2.5uS for it to settle and my filter cap to charge. Thanks for your help so far.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-14 07:29 AM

Will the triple simultaneous mode with 2 channels per ADC result in a conversion time as per my previous post?

In triple simultaneous mode, all 3 ADCs will sample and convert in parallel. The total conversion time will be 30 cycles to convert 5 inputs (plus 1 dummy because 3x2=6). You will need to use DMA for this. The conversions will end up in a 6 word 16 bit memory buffer you designate. You will have to extract the 5 conversions of interest before the next sample.What prescale of ADCCLK should I use...? Whatever converts APB2 clock to less than or equal to the maximum allowable ADCCLK. See the datasheet for allowable ADCCLK values. I believe the ADCCLK is what paces conversion time, not APB2 clock. Cheers, Hal- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-14 04:43 PM

Thanks Hal.

So am I right in understanding each channel does not have an independent sample and hold? Just the 3 (1 in each of the ADCs). That's a shame, would have been good to do all 5 samples in parallel and then convert sequentially in groups of 3 as you said. Stive- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-14 05:17 PM

So am I right in understanding each channel does not have an independent sample and hold?

Yes. This is probably a good time for you to read (or re-read) the F4 Reference Manual ADC section. Cheers, Hal- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-14 08:58 PM

''....each channel does not have an independent sample and hold? Just the 3 (1 in each of the ADCs).That's a shame,.....''

The SAR ADC implementation is done internally using capacitor banks. It is space consuming in silicon. As far as i know all MCUs in this world have single Sample-Hold circuit per ADC, the multiple channel are however available..- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-06-14 11:13 PM

I don't know your control concept, but it might not be necessary to use the ADC at all.

If you just need to know if the voltage (or voltage drop for current measurement) exceeds a certain level, you can use an external comparator. You could use the DAC to set the threshold level(s). We use this approach for multichannel lighting converters, which have some similiarities to your application, and work in the about same frequency range. These are mass products, so we use slow 8 Bit controllers, no Cortex M4...- ADC multichannel with DMA with more than 8 ADC channel in STM32CubeMX (MCUs)

- Feedback Requested on general approached used for ADC in STM32 MCUs products

- HAL ADC multi channel in polling mode in STM32 MCUs Embedded software

- Measuring elapsed time in nanoseconds in STM32 MCUs products

- ADC Interrupt Callback in STM32 MCUs products