- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Does framing error make sense if you are tx'ing ? ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Does framing error make sense if you are tx'ing ? dma question

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-17 12:48 PM

Hello All, hope you are doing well Clive.

I dont know if i've always had this issue but I always get a FE int in my DMA1_Stream6, but I only use that dma for transmitting. From what I understand a framing error would be on the receiving end of things right ? Thanks !- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-17 01:10 PM

In the context of a USART perhaps, not so sure what it means with DMA, where there are two sides to the transaction (Read / Write), an uninformed guess might be that it relates to the memory alignment of one of the transfers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

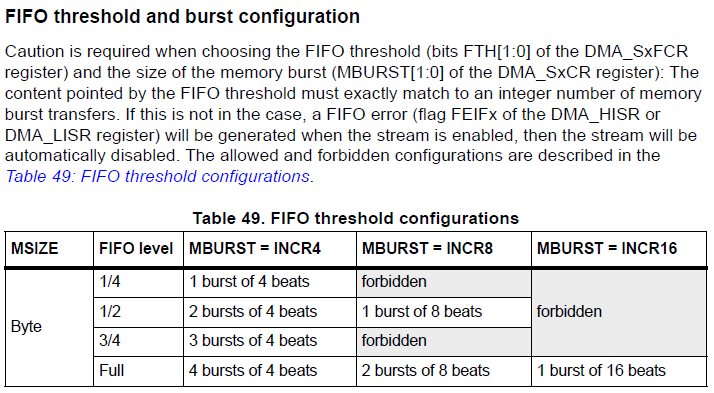

2014-02-17 01:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-17 01:34 PM

Well that makes sense, no wonder I could not make heads or tails of it. I keep looking at ''framing error''.

Thanks Clive, now I know where to start looking. I think what you wrote means something along the lines of I need to have a divisible by X number of bytes to transmit. I'm already padding out some bytes to make a CRC so it must be divisible by 4. I'll investigate more in the fifo area ! This is the code in case your curious.DMA_InitStructure.DMA_Channel = DMA_Channel_4;

DMA_InitStructure.DMA_PeripheralBaseAddr = (uint32_t)&(USART2->DR);

// usart2 data register

DMA_InitStructure.DMA_Memory0BaseAddr = (uint32_t)&FrameBuffer[mPacketTransferIter*MAX_PACKET_SIZE];

mPacketTransferIter++;

// this will make our array point to the next chunk

DMA_InitStructure.DMA_DIR = DMA_DIR_MemoryToPeripheral;

// if we need to transfer more then only send up to max packet size

if

(mBytesLeftToTransfer > MAX_PACKET_SIZE)

{

DMA_InitStructure.DMA_BufferSize = MAX_PACKET_SIZE;

mBytesLeftToTransfer = (mBytesLeftToTransfer - MAX_PACKET_SIZE);

}

else

{

// else send whats left !

DMA_InitStructure.DMA_BufferSize = mBytesLeftToTransfer;

mBytesLeftToTransfer = DONE_BYTES;

// set this so we know its the end

}

DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Disable;

DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable;

DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_Byte;

DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_Byte;

DMA_InitStructure.DMA_Mode = DMA_Mode_Normal;

DMA_InitStructure.DMA_Priority = DMA_Priority_VeryHigh;

DMA_InitStructure.DMA_MemoryBurst = DMA_MemoryBurst_Single;

//DMA_InitStructure.DMA_FIFOMode = DMA_FIFOMode_Enable;

//DMA_InitStructure.DMA_FIFOThreshold = DMA_FIFOThreshold_Full;

DMA_InitStructure.DMA_PeripheralBurst = DMA_PeripheralBurst_Single;- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-17 01:35 PM

Well that makes sense, no wonder I could not make heads or tails of it. I keep looking at ''framing error''.

Thanks Clive, now I know where to start looking. I think what you wrote means something along the lines of I need to have a divisible by X number of bytes to transmit. I'm already padding out some bytes to make a CRC so it must be divisible by 4. I'll investigate more in the fifo area ! This is the code in case your curious.DMA_InitStructure.DMA_Channel = DMA_Channel_4;

DMA_InitStructure.DMA_PeripheralBaseAddr = (uint32_t)&(USART2->DR);

// usart2 data register

DMA_InitStructure.DMA_Memory0BaseAddr = (uint32_t)&FrameBuffer[mPacketTransferIter*MAX_PACKET_SIZE];

mPacketTransferIter++;

// this will make our array point to the next chunk

DMA_InitStructure.DMA_DIR = DMA_DIR_MemoryToPeripheral;

// if we need to transfer more then only send up to max packet size

if

(mBytesLeftToTransfer > MAX_PACKET_SIZE)

{

DMA_InitStructure.DMA_BufferSize = MAX_PACKET_SIZE;

mBytesLeftToTransfer = (mBytesLeftToTransfer - MAX_PACKET_SIZE);

}

else

{

// else send whats left !

DMA_InitStructure.DMA_BufferSize = mBytesLeftToTransfer;

mBytesLeftToTransfer = DONE_BYTES;

// set this so we know its the end

}

DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Disable;

DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable;

DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_Byte;

DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_Byte;

DMA_InitStructure.DMA_Mode = DMA_Mode_Normal;

DMA_InitStructure.DMA_Priority = DMA_Priority_VeryHigh;

DMA_InitStructure.DMA_MemoryBurst = DMA_MemoryBurst_Single;

//DMA_InitStructure.DMA_FIFOMode = DMA_FIFOMode_Enable;

//DMA_InitStructure.DMA_FIFOThreshold = DMA_FIFOThreshold_Full;

DMA_InitStructure.DMA_PeripheralBurst = DMA_PeripheralBurst_Single;- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-17 03:15 PM

I've tried several ''fifo'' modes and settings, I always get the FE along with TC. I think this is because the last bytes we transfer are not on the 32 byte boundry ?

I'm going to refactor my code to byte stuff till its %32 == 0 (instead of %4). Will take me a while but maybe it will help the DMA work :\- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-17 06:27 PM

I still get a FE no matter what I do. I've made sure the data I'm sending out is divisible by 32 thinking that would resolve any issues the DMA may have. There is not one example using DMA with USART for TX.

Closest I can find does this, which makes no sense to me. Why disable ?00217 DMA_InitStructure.DMA_FIFOMode = DMA_FIFOMode_Disable ;

00218 DMA_InitStructure.DMA_FIFOThreshold = DMA_FIFOThreshold_1QuarterFull ;

00219 DMA_InitStructure.DMA_MemoryBurst = DMA_MemoryBurst_Single ;

00220 DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_Byte;- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-18 04:27 PM

I reduced my dmatx function to its pure essence and I send out a fixed packet of 384 bytes and I still get a TE interrupt. I get it when ntdr is 0. Its weird when I hit the first bp on the isr TC is not set but shortly after it is. So its hard to tell if TE is set then TC just after or if they are always getting set at the same time.

void restartCommDMATX(u8* FrameBuffer,int start, int size)

{

DMA_InitTypeDef DMA_InitStructure;

DMA_DeInit(DMA1_Stream6);

DMA_InitStructure.DMA_Channel = DMA_Channel_4;

DMA_InitStructure.DMA_PeripheralBaseAddr = (uint32_t)&(USART2->DR); // usart2 data register

DMA_InitStructure.DMA_Memory0BaseAddr = (uint32_t)&FrameBuffer[start];

DMA_InitStructure.DMA_DIR = DMA_DIR_MemoryToPeripheral;

DMA_InitStructure.DMA_BufferSize = size;

DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Disable;

DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable;

DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_Byte;

DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_Byte;

DMA_InitStructure.DMA_Mode = DMA_Mode_Normal;

DMA_InitStructure.DMA_Priority = DMA_Priority_VeryHigh;

// FIFO

DMA_InitStructure.DMA_MemoryBurst = DMA_MemoryBurst_Single;

DMA_InitStructure.DMA_FIFOMode = DMA_FIFOMode_Disable;

DMA_InitStructure.DMA_FIFOThreshold = DMA_FIFOThreshold_1QuarterFull;

DMA_InitStructure.DMA_PeripheralBurst = DMA_PeripheralBurst_Single;

// init the dma

DMA_Init(DMA1_Stream6, &DMA_InitStructure);

USART_DMACmd(USART2, USART_DMAReq_Tx, ENABLE);

// setup transfer complete int, and error init

DMA_ITConfig(DMA1_Stream6, DMA_IT_TC, ENABLE);

DMA_ITConfig(DMA1_Stream6, DMA_IT_FE, ENABLE);

DMA_ITConfig(DMA1_Stream6, DMA_IT_TE, ENABLE);

// start the dma transfer, it will execute now

DMA_Cmd(DMA1_Stream6, ENABLE);

}- Question about frame format of sai in STM32 MCUs Other solutions

- What could be causing the STM32L152 UART Rx interrupt to intermittently not fire when data arrives and interrupts are correctly configured? in STM32 MCUs Embedded software

- Partial Frame Buffer documentation question in STM32 MCUs TouchGFX and GUI

- I use STM32F030R8T8 programming with CUBE and TrueStudio. I have a problem with the frame error in UART communication on RS485 line. I have implemented the error_callback function to reset the error, but receiving remains blocked. in STM32 MCUs products

- Hi, I have a question concerning CAN 2 of the STM32F446RE. I want to use CAN 1 and CAN 2. I can recieve and send framewith the CAN 1. But I don't know how I can recieve frame with the CAN 2. I don't find how configure filters and interupt on CAN 2 in STM32 MCUs products