Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- F2/F4 I2S Ext.Clock

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

F2/F4 I2S Ext.Clock

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-03 05:19 AM

Posted on April 03, 2013 at 14:19

Hi friends,

It is written at ref/man for F2 and F4:Bit 7:0 I2SDIV: I2S Linear prescaler

I2SDIV [7:0] = 0 or I2SDIV [7:0] = 1 are forbidden values. Why ''0'' is forbidden is clear, but why ''1'' ?! I make some intensive tests, and with I2SDIV=1 it works fine, did not see any problem. Usially, I not like to use the components ''out of spec'', for clear reason, but I want to understand the spec. This issue I don't understant, so I have to decide - or use it out of spec, or to double the clock frequency Ithat increase the device' cost). Mayby DIV=1 has a problem only with internal PLL clock? Thanks. #stm32-i2s

Labels:

- Labels:

-

I2S

3 REPLIES 3

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-04 02:12 AM

Posted on April 04, 2013 at 11:12

> I make some intensive tests, and with I2SDIV=1 it works fine, did not see any problem.

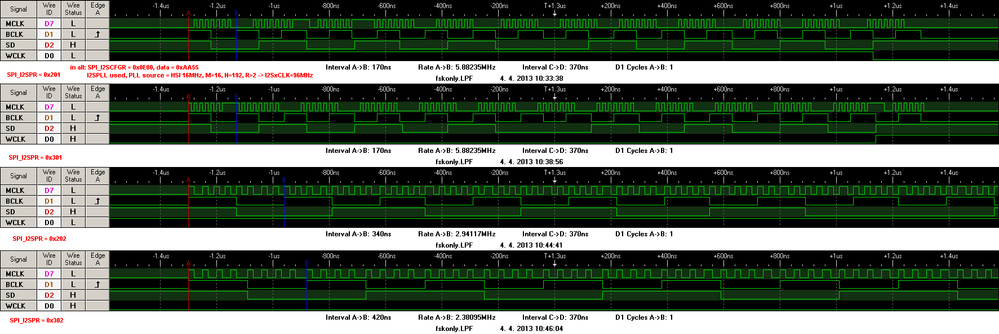

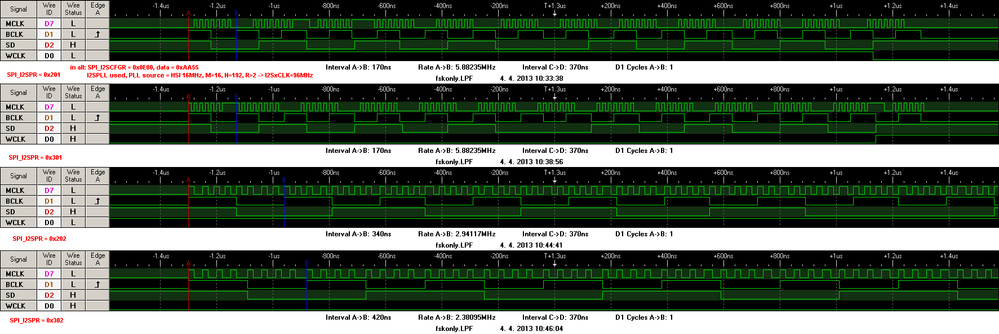

Probably not intensive enough - I do see problems - with I2SDIV=1 , ODD=1 appears to be ignored. This is not to say that I2SDIV=1 and ODD=0 will work under any circumstances. (The missing MCO pulses are due to sampling rate of LA set to too low - 100MHz - sorry). JW

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-04 08:10 AM

Posted on April 04, 2013 at 17:10

Can you check with ODD=0? I do not use it.

However, if I set DIV=1 and after this I chahged the format (I2S-LJ-RJ) sometimes I have seen the shift for a whole byte or even half-word, but if I don't change format and change Fs only - all OK. After this I make the following: Init I2S with DIV-2 and format setting, 5ms delay, then init I2S again, with the same format but DIV=0. With this - never seen bit/byte/half-word shift. All this just for fan, I'm afraid to use it in a production device, so I increase Ext.Freq twice.Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-04-05 04:04 AM

Posted on April 05, 2013 at 13:04

> Can you check with ODD=0? I do not use it.

The first and third waveforms were taken with ODD=0 - the whole SPI_I2SPR register is given under each waveform. JW