- STMicroelectronics Community

- Automotive & Transportation

- Microcontrollers

- Im working for bootloader on SPC564A80B4. Facing i...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Im working for bootloader on SPC564A80B4. Facing issues in system clock generation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-21 09:58 PM

Hello, I configured in enhanced mode for system clock generation, our input clock is 40Mhz external crystal and need to generate 150Mhz system clock. Since hardware is not supported to check CLKOUT pin for system clock, we configured SCK clock for calculating system clock.

- In below code used as provided by ST, but we facing a problem in free running the code ( debug port fail) while debugging the code in TRACE32.For below configuration, code is running some exceptional condition. No system clock generation.FMPLL.ESYNCR2.R = 0x00000001;FMPLL.ESYNCR1.R = 0xF005002Dwhile (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK */ FMPLL.ESYNCR2.R = 0x00000000;

NOTE: For above configuration the parameters values EPREDIV, ERFD and EMFD is not satisfying for 150Mhz system clock generation if we substitute in enhanced mode formula. Im confused!!!!!

- In below code used as provided by ST, but we facing a problem in free running the code ( debug port fail) while debugging the code in TRACE32. For below configuration, code is running some exceptional condition. No system clock generation. FMPLL.ESYNCR2.R = 0x00000000; FMPLL.ESYNCR1.R = 0xF005002D; while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK */ FMPLL.ESYNCR2.R = 0x00000000;

- In below code we referred reference manual of SPC564A80B4. Here we not facing problem debug port fail. The code is free running in debug condition.For below configuration, system clock is 72MhzFMPLL.ESYNCR2.R = 0x00000001;FMPLL.ESYNCR1.R = 0xF005002Dwhile (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK */ FMPLL.ESYNCR1.R |= 0x70000000;

- In below code we referred reference manual of SPC564A80B4, but we facing a problem in free running the code ( debug port fail) while debugging the code in TRACE32.For below configuration, system clock is 150Mhz.FMPLL.ESYNCR2.R = 0x00000000;FMPLL.ESYNCR1.R = 0xF005002Dwhile (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK */ FMPLL.ESYNCR1.R |= 0x70000000;

Please do needful and give us solution resolve this issue, the project is in critical condition. If any documents related to issue please do share to my ID below mentioned.

Regards

Mahesh chamaraja

Office ID :

mailto:mahesh.chamaraja@kpit.com

Phone No : +917259205624

##clock ##spc56 ##fmpllSolved! Go to Solution.

- Labels:

-

RCC

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-02-21 02:41 AM

Hello Mahesh ,

sorry the RM is not cleared

You should respect some steps

Step 1

Support for 50MHz system clock generation

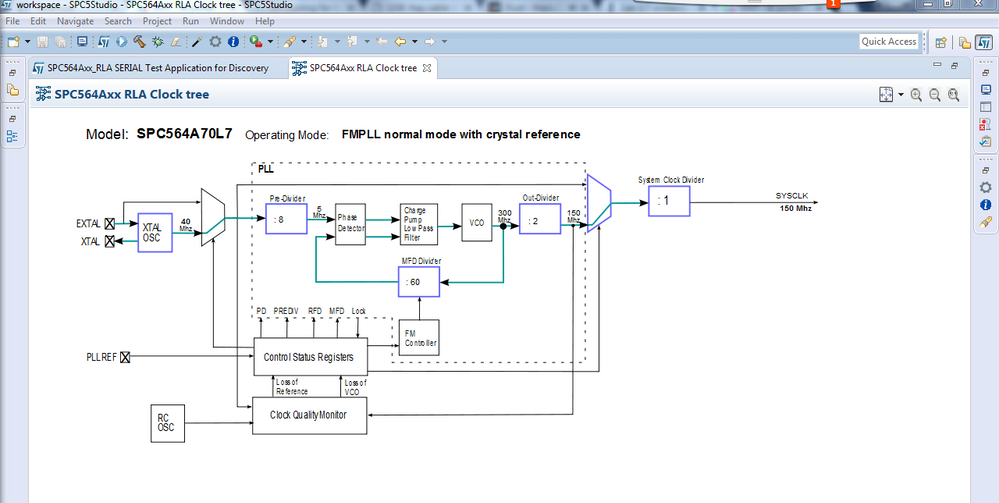

The oscillator and PLL support generation of a 150 MHz system clock while using the 40 MHz crystal required for FlexRay operation. A possible PLL configuration is shown below: �?Input clock (crystal frequency): 40 MHz

�? EPREDIV/IDF divider = /8 (1–15 range supported) �? EMFD/NDIV loop divider = 80 (32–96 supported) �? VCO clock out = 300 MHz (256–512 MHz range supported) �? ERFD/ODF output divider = /2 (/2, /4, /8, /16 supported) �? SYSDIV divider = /1 (/1, /2, /4, /8, /16 supported) �? System clock = 50 MHzStep 2

wait for Lock the PLL

Step 3

Support for 50MHz system clock generation

The oscillator and PLL support generation of a 150 MHz system clock while using the 40 MHz crystal required for FlexRay operation. A possible PLL configuration is shown below: �?Input clock (crystal frequency): 40 MHz

�? EPREDIV/IDF divider = /8 (1–15 range supported) �? EMFD/NDIV loop divider = 60 (32–96 supported) �? VCO clock out = 300 MHz (256–512 MHz range supported) �? ERFD/ODF output divider = /2 (/2, /4, /8, /16 supported) �? SYSDIV divider = /1 (/1, /2, /4, /8, /16 supported) �?System clock = 150 MHz

Step 4

wait for Lock the PLL

==> It is ok for my side

/**

* @brief SPC563 clocks and PLL initialization.

* @note All the involved constants come from the file @Community memberoard.h and

* @p hal_lld.h

* @note This function must be invoked only after the system reset.

*

* @special

*/

void spc_clock_init(void) {

#if !SPC5_NO_INIT

/* PLL activation.*/

FMPLL.ESYNCR1.B.EMODE = 1; /* Enhanced mode on. */

FMPLL.ESYNCR1.B.CLKCFG &= 1; /* Bypass mode, PLL off.*/

#if !SPC5_CLK_BYPASS

FMPLL.ESYNCR1.B.CLKCFG |= 2; /* PLL on. */

FMPLL.ESYNCR1.B.EPREDIV = SPC5_CLK_PREDIV;

FMPLL.ESYNCR1.B.EMFD = SPC5_CLK_MFD;

FMPLL.ESYNCR2.B.ERFD = SPC5_CLK_RFD;

while (!FMPLL.SYNSR.B.LOCK)

;

FMPLL.ESYNCR1.B.EMFD = 60;

while (!FMPLL.SYNSR.B.LOCK)

;

FMPLL.ESYNCR1.B.CLKCFG |= 4; /* Clock from the PLL. */

#endif /* !SPC5_CLK_BYPASS */

/* SYS Clock Divider setting.*/

#if (SPC5_SIU_SYSDIV_BYPASS == TRUE)

SIU.SYSDIV.B.BYPASS = 1U;

#else

SIU.SYSDIV.B.BYPASS = 0U;

SIU.SYSDIV.B.SYSCLKDIV = (uint8_t)SPC5_SIU_SYSDIV_SYSCLKDIV;

#endif

/* Setting up RAM/Flash wait states and the prefetching bits.*/

ECSM.MUDCR.R = SPC5_RAM_WS;

FLASH_A.BIUCR.R = SPC5_FLASH_BIUCR | SPC5_FLASH_WS;

FLASH_A.BIUCR2.R = 0;

#if !defined(_SPC564A70_)

/* The second controller is only present in Andorra 3M or 4M.*/

FLASH_B.BIUCR.R = SPC5_FLASH_BIUCR | SPC5_FLASH_WS;

FLASH_B.BIUCR2.R = 0;

#endif /* !defined(_SPC564A70_) */

/* CAN Clock Divider setting.*/

SIU.SYSDIV.B.CAN_SRC = (uint8_t)SPC5_SIU_SYSDIV_CAN_SRC;

#endif /* !SPC5_NO_INIT */

}

�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?Best regards

Erwab

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-24 05:46 AM

Hello Mahesh ,

ESYNCR2 is often used in order to set the Enhanced reduced frequency Divider

Enhanced reduced frequency divider

This 2-bit field controls a divider at the output of the FMPLL. The value specified by the ERFD bitsestablishes the division factor applied to the FMPLL frequency.00 Divide by 201 Divide by 410 Divide by 811 Divide by 16You have to check if the different transition is going respect on the supported range.

- Input clock frequency range from 4 MHz to 20 or 40 MHz(p) before the predivider, and from 4 MHz to 16 MHz after the predivider

- Voltage controlled oscillator (VCO) range from 256 MHz to 512 MHz

- VCO free-running frequency range from 25 MHz to 125 MHz

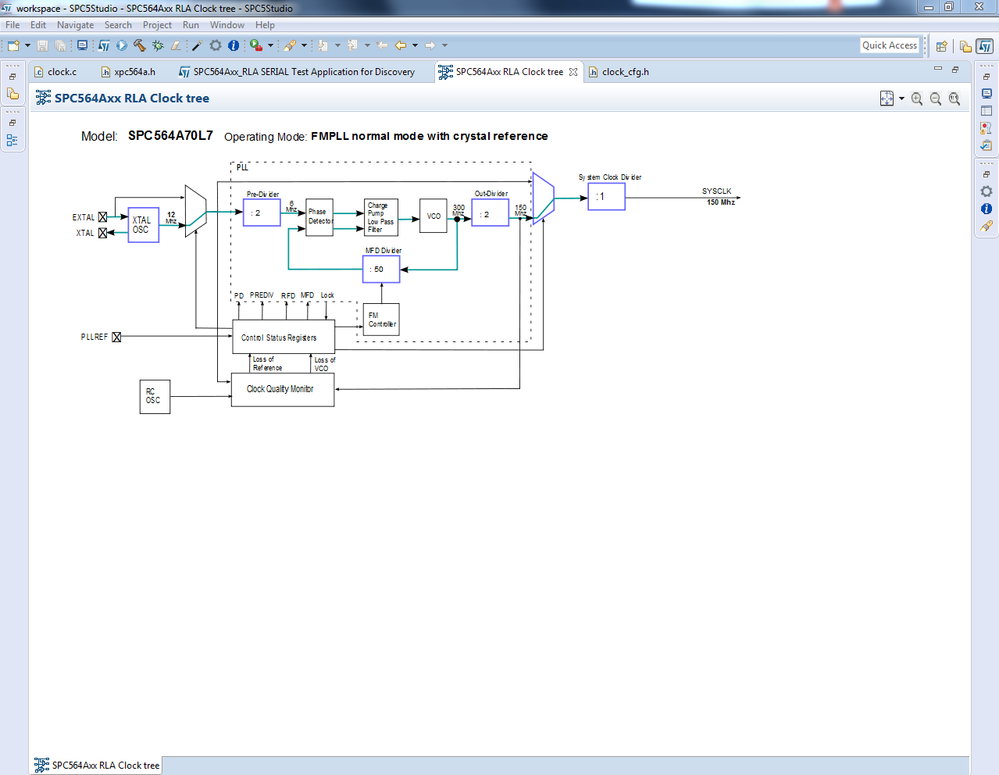

You can use SPC5Studio (SPC564A80B4 ClockTree) and enter your own values :

Take any application from Application Wizard

Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-24 08:53 PM

Hellow Erwan,

Clock configuration :

FMPLL.ESYNCR2.R = 0x00000001;/*ERFD->2*/

FMPLL.ESYNCR1.R = 0xF007003C;/*EPREDIV->8,EMFD->60*/ while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK */ FMPLL.ESYNCR1. R |= 0x70000000;/*Again configured normal mode with crystal reference*/I got system clock 74.88Mhz, verified system frequency by generating SCK frequency

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-24 09:02 PM

Hello Erwan,

Clock configuration we following :

ECSM.MUDCR.R = 0x40000000; /* 1 SRAM waitstate for fsys above 98MHz */

FMPLL.ESYNCR2.R = 0x00000001;/*ERFD->2*/

FMPLL.ESYNCR1.R = 0xF007003C;/*Enhanced mode, EPREDIV->8, EMFD->60*/while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK */FMPLL.ESYNCR1. R |= 0x70000000;/*Again configured normal mode with crystal reference*/SYSDIV if bypassed (divide by 1).

I got system clock 74.88Mhz, verified system frequency by generating SCK frequency since hardware not supported to check.

Please suggest any modification in configuration of crystal. Any information you need let me know.

Regards and thanks

Mahesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-25 03:20 AM

According to your configuration ,

Indeed your sysclock should be 75 MHz

do you want 150MHz ?

According to the RM, MPLL.ESYNCR2.R = 0x00000001;/*ERFD->2*/ ==> 75 Mhz

According to the RM, MPLL.ESYNCR2.R = 0x00000000;/*ERFD->1*/ ==> 150 Mhz is correct too.

should be correct.

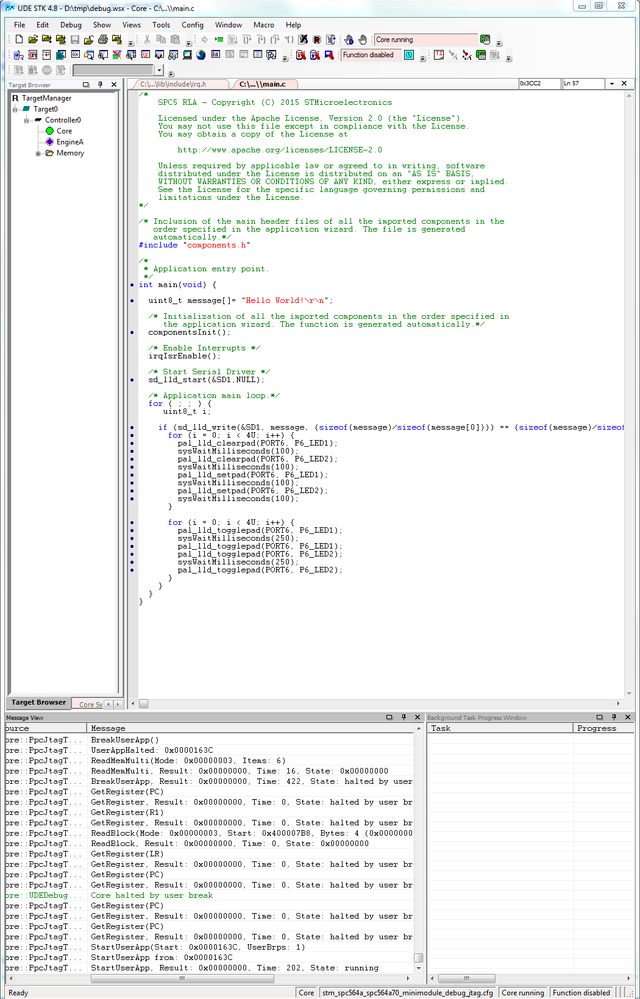

I am checking your configuration with PLS Debugger and with a basic Test Application

Best Regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-25 05:47 AM

Exactly you are right:

ESYNCR2.R=0x00000001;/*75Mhz & code free running under debugging condition in

TRACE32

*/ESYNCR2.R=0x00000000;/*150Mhz, But in this case free running not happening Im facing debug port fail in TRACE32 */

Im suspecting is that initialisation of clock its not proper? or else we meeting system frequency which cause this type of error(debug port fail)?

Regards and Thanks

Mahesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-25 05:59 AM

Hello Manesh ,

Your clock configuration is good.

I have tried with PLS Environment & SPC5STudio 5.0 with SPC564A70L7

it is ok , no problem with flash , debug.

You should focus your investigation on TRACE32 / LAUTECHBACH.

I am checking with an other team which uses TRACE32.

Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-25 07:11 AM

Hello Erwan,

Thank you for quick response.

Do you suspect any mistake in code or configuration other than OSC? We using one millisec timer and internal watchdog thats all.

Erwan can you help us on issue we are facing FlexRay communication driver development. I posted it please check this issue is blocking our further development.

Regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-26 08:22 AM

Hello Manesh ,

1 ms timer and internal Watchdog are not a problem

regularly in SPC5Studio and SPC56 Family, we use 1ms tick timer on PIT (Chibios , NIL and Os-Less)

For the debugger , you should disable the Watchdog before connect on PLS

TRace32 it should be the same.

// disable watchdog

SET SWT_SR 0xC520 SET SWT_SR 0xD928 SET SWT_CR 0xFF00000AFor FlexRay, you should take care of the clock and the status error of the Flexray controller.

https://community.st.com/0D50X00009XkYOzSAN

Best Regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-27 01:31 AM

Hello Erwan,

I tried with disabling watchdog, I getting same frequency 74.88Mhz.

I confused why free running in not happening and we get error debug port fail if I alter

ESYNCR2.R=0x00000001; to

ESYNCR2.R=0x00000000;.

Regards

Mahesh