- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32F4 PLL I2S continous clock generation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F4 PLL I2S continous clock generation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-11 03:13 PM

Hello,

i have a question about MCLK and LRCK generation on an STM32F4 system.I want to connect an Audio ADC to an SPDIF codec which need an continousMclk and Lrclock. I have the option to use an external 24.5760 Meg crystal and dothe LRClock phaseadjustment via ttl logic /divider to keep all in sync.What i need is the I2S_MCLK and I2S_WS (LRCLK) clocks to remain active even when i amnot sending bytes or receive some.I have not found any information on how to route the PLL clock to an I/O pin.Is this possible and do i have jitter improvements or should i keep the crystal ?Big thanks !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-15 12:46 PM

I want to connect an Audio ADC to an SPDIF codec

What exactly is the role of STM32 in this? Can you draw a block schematics, indicating the interconnections and the expected source of clocks and data?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-16 12:38 AM

Hello Jan, thanks for reply. I want to use the STM32 for USB Audio stuff.

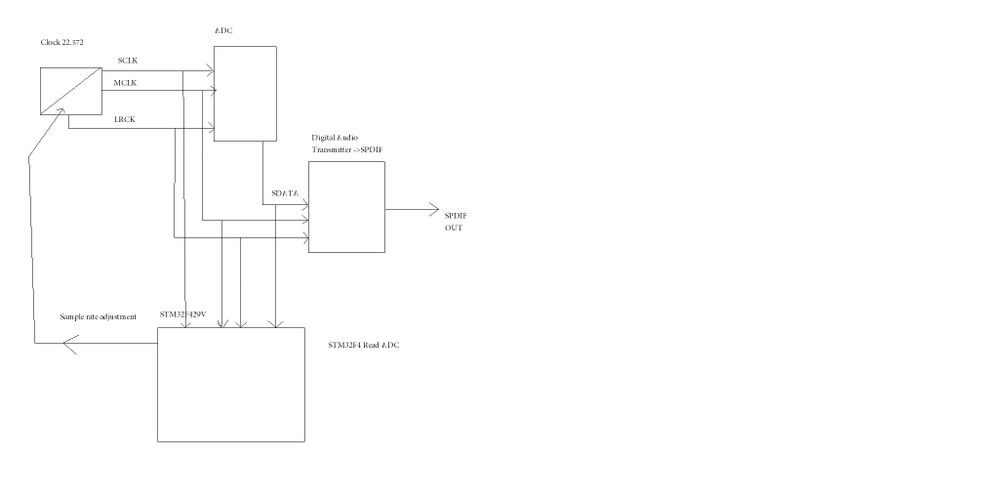

Please find a block diagram attached. Goal is to replace the clocking circuit (mclk,lrck,slck)by the STM32 PLLI2S. Becauseits much easier to adjust the needed samplerates on the STM32 and i save some control ports.As far as i know continous clocking is only possible by sending zero bytes to the I2S.STM32 read of the adc datas shouldbe possible in this configuration.Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-16 03:54 AM

Big thanks Jan, to point me to the right direction. I have just read the RCC section of the STM32F429 i can output a PLLI2S clock on pin PC9.That

helps me a lot and is a nice external board clocking feature. I will try it with some of my discoverys. I hope i can change the pll clock on the fly. Oh i see... Mclk is output only

Thanks again Jan.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-16 04:02 AM

Hans,

this arrangement - I2S in STM32 acts purely as a slave - of course has no chance not to work... (as long as the external SCLK is *permanently* 16 or 32 ticks per LRCK flip - inserting or removing a single SCLK needs you'll need to restart the I2S in STM32 - in this the I2S in STM32 does not implement the protocol properly, ie. it does not restart its internal bitcounter upon every LRCK=WS edge, see errata).

You don't need to connect MCLK to STM32 at all - MCLK is needed only in the ADC and DAC for the digital reconstruction filters; I2S as a digital interface needs only SCLK and LRCK.

--

You can use STM32 also as a master and clock source if you set I2S as a master. I honestly don't know if clock generation in master receiver requirest continuous writing to the data register - probably not, and it's easy to try, but even if it would, a simple DMA in circular mode would take care of it with no need for software intervention.

In the 'F407, there is a dedicated I2S PLL. You can output its clock directly onto some of the MCO pins, see the RCC chapter (the block schematic at its beginning is very useful in these questions). However, you don't need that - the PLL feeds into the I2S which can output a properly divided MCLK onto one of the pins (and then both SCLK and LRCK of course).

I am not sure whether the I2S PLL in STM32 can be fine-tuned on the fly.

JW

- CubeMX code / USB Audio class / Correct management of DMA callbacks between Driver BSP, USB audio? in STM32 MCUs products

- I2S MASTER desynchronization at start in STM32 MCUs products

- Generic STM32F4 series is not working on Raspberry pi via STM32CubeProgrammer(Serial) in STM32 MCUs products

- SOLVED: IS BUG. STM32f4 custom hid generated code shows up as "STMicroelectronics LED badge -- mini LED display -- 11x44". where is this configuration fault? in STM32CubeIDE (MCUs)

- STM32CubeMX 6.8.0 released in STM32CubeMX (MCUs)