- STMicroelectronics Community

- Missing nodes

- missing-QuestionPost

- Capture timestamps on falling edge events with eTi...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Capture timestamps on falling edge events with eTimer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-17 08:03 AM

Hello everyone,

I work on a SPC560 P40 L3 and I would to capture timestamps on falling edge events on SECSRC ''Counter #0 input pin''.

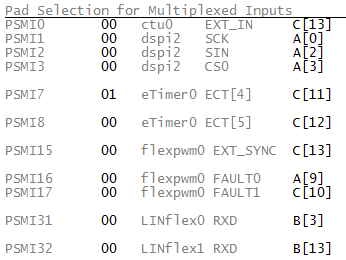

I have one square signal mapped on eTimer0 channel 0 on the C[11] pin alternate function.

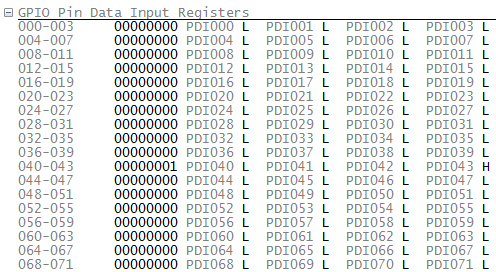

I could see my signal shift from high state to low state with Trace 32. So I think my signal is correctly mapped to the input.

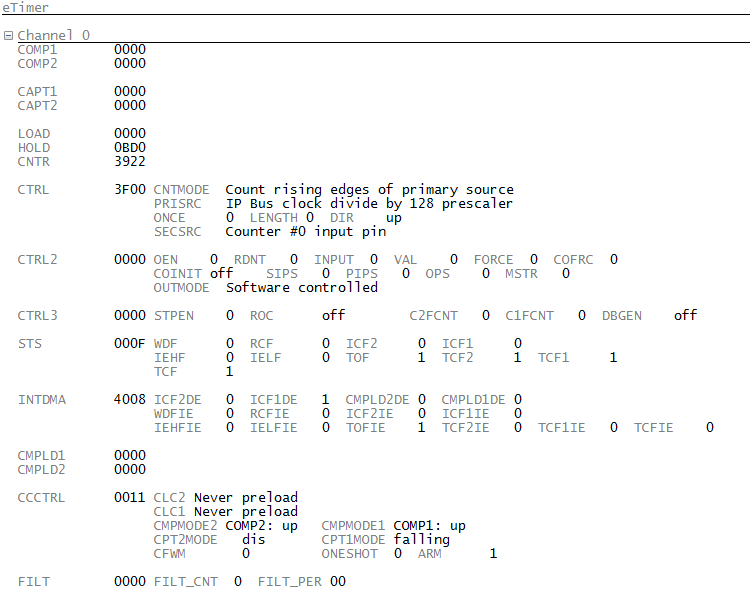

Here is my eTimer channel 0 configuration :

I have a signal with a 12,5 kHz tick time and a 16 Mhz SYSCLOCK.

Unfortunately, there is no events on CAPT 1 register.

First, I was wondering for some time synchronization issues but when I select ''Count rising edges of primary source while secondary input high active'' CNTR just stop. So I suspect that the counter #0 input pin is not linked with my input signal. I could manually see values on CAPT 1 when I change SECSRC polarity with the SIPS register, but thats all.

Is there any mistakes with my eTimer configuration register ? I am also wondering how I could synchronize IP bus clock and my sensor signal tick time with just a 128 prescaler.

Thanks.

Best regards,

Florent Plazas

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-23 01:47 AM

Hello everyone,

After 2 weeks of debugging, I figured out that ETC[N] pad are linked with 'Counter #N Input pin'.

So if you decide to use the 'ETC[4]' pin for eTimer0 input source, you have to choose 'Counter #4 Input pin' register.

I think you may clarify that in the table N°373 in the SPC560P34..40 reference manual.

I never saw any acronym definition for 'ETC[N]' (ETC = E Timer Counter [N] ?).

Best regards,

Florent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-23 01:47 AM

Hello everyone,

After 2 weeks of debugging, I figured out that ETC[N] pad are linked with 'Counter #N Input pin'.

So if you decide to use the 'ETC[4]' pin for eTimer0 input source, you have to choose 'Counter #4 Input pin' register.

I think you may clarify that in the table N°373 in the SPC560P34..40 reference manual.

I never saw any acronym definition for 'ETC[N]' (ETC = E Timer Counter [N] ?).

Best regards,

Florent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-23 04:59 AM

Hello Florent ,

Sorry for not helping you earlier.

yes , i am agreed with you Table 373 is not clear.

i have escalated your point in the Technical Writer team.

Do not hesitate to use the Pinmap Wizard in SPC5Studio

Best Regards

Erwan