- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- RTC smooth calibration on STM32L072CZ

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RTC smooth calibration on STM32L072CZ

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-03 11:32 AM

Hi all,

Summary: With external 32.768kHz crystal and RTC PREDIV_S=32767 and PREDIV_A=0 I cannot RTC configure smooth calibration correctly, specifically it seems impossible to set the CALP bit in the CALR register.

Details:

I am working on a project at the moment using the STM32L072CZ as part of the Murata

CMWX1ZZABZ-091 module on the

B-L072Z-LRWAN1 LoRa board. Our application uses the HAL and drivers from the

1.1.4 package. The RTC is clocked from the external 32768Hz crystal.For various reasons we needed to reduce the timestep used for the subsecond register in the RTC from the default of 0.976ms (PREDIV_S=1023, PREDIV_A=31). We initially tried the maximum (PREDIV_S=32767, PREDIV_A=0) which gives a timestep of 0.03ms, which works perfectly at the expense of more power. The issue is that this has broken the smooth calibration functionality. Digging into it we appear to have a problem with setting the RTC CALR register in HAL_RTCEx_SetSmoothCalib(). Specifically it seems to be impossible to set the CALP bit. For example if we want to add 5 clock pulses over a 32 second period we would call this function with the +512 pulses flag set and the minus pulses set to 507. This should result in CALR =0x81fb, but it is actually set to 0x1fb. The same can be seen by manually changing the register in the debugger (after the registers have been unlocked).

The same code works fine with a 0.976ms timestep

(PREDIV_S=1023, PREDIV_A=31) and it also appears to work with a 0.122ms timestep (PREDIV_S=8191, PREDIV_A=3).

Has anybody else encountered this?

Thanks

Jonathan♯♯

#stm32l0 #rtc #smooth-calibrationSolved! Go to Solution.

- Labels:

-

RTC

-

STM32L0 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-03 01:52 PM

Has anybody else encountered this?

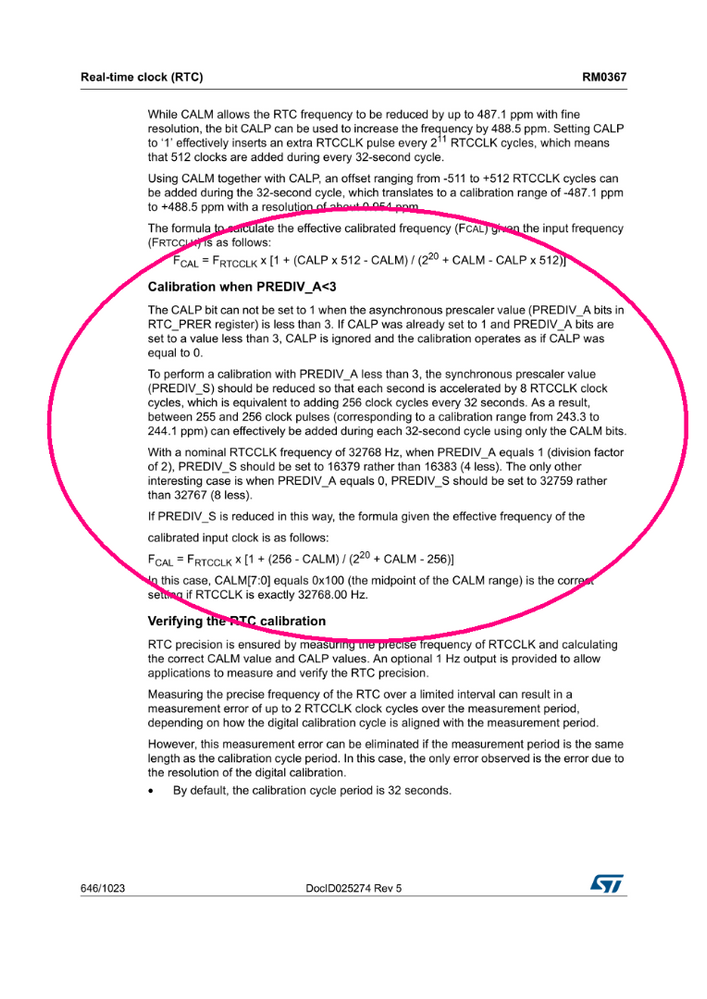

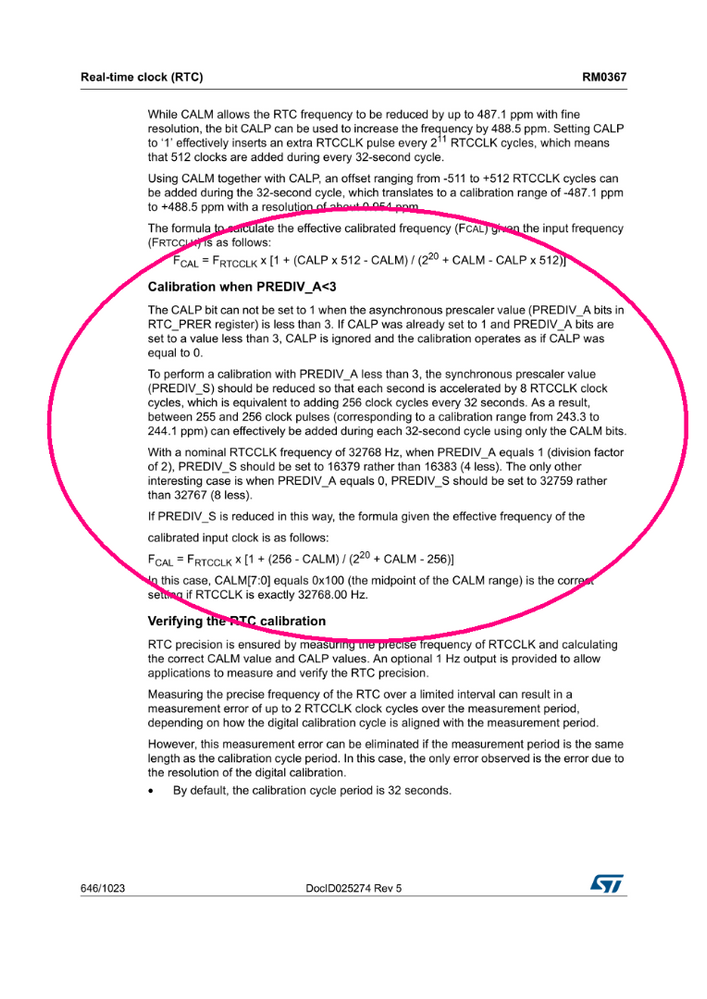

The chip developers have, apparently:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-03 01:52 PM

Has anybody else encountered this?

The chip developers have, apparently:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-04 03:16 AM

How on earth did I miss that! Thanks for pointing out the obvious .

- RTC smooth calibration on STMF446 in STM32 MCUs Embedded software

- I'm currently try to set up a project for smooth calibration on a Nucleo-L476 like in the smooth Calibration example AN4759. Same Board, same code but it doesn't work. Do you may have a guidline or ioc file? in STM32CubeMX (MCUs)

- Unable to calculate the correct smooth calibration value for the RTC on an STM32F411. Can you spot my error? in STM32 MCUs products

- RTC smooth calibration and verification? in STM32 MCUs products

- stm32 RTC RTC smooth digital calibration. Is there a table listing CALP&CALM values and related ppm? I want to a lookup table. in STM32 MCUs products