- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Working with TIM Output Compare

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Working with TIM Output Compare

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-16 02:08 PM

I try to generate pulses for the stepping motor at the Output Compare output.

The time between their leading fronts varies (acceleration / deceleration).The control of delays based on the well-known principle: free run 16-bit timebase counter with modulus of 65536.The delay is formed by updating the CC register, adding the delay duration to the previous CC value.Two CC channels are used, operating with a fixed time shift.First, CC2 is triggered; its interrupt performs calculations and check conditions to make a step.Then CC1 is triggered to form the front of the step pulse, if needed.CC3 and CC4 channels are reserved for second stepping motor but not used.However, I can not start these interrupts in the required sequence.

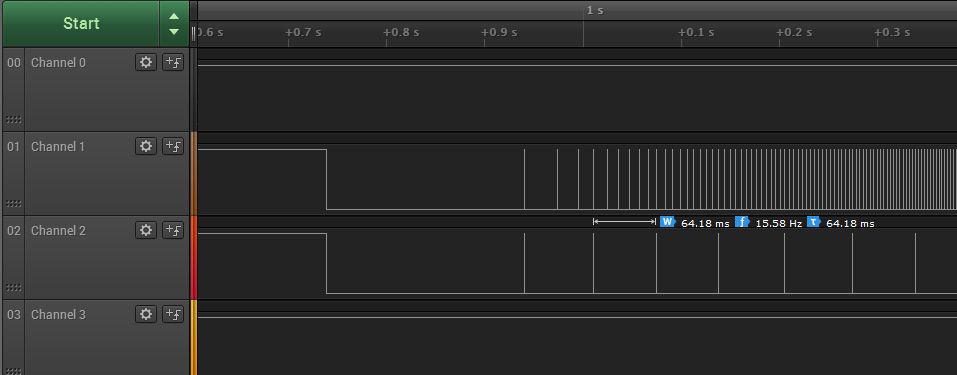

Now I'm stuck with the fact that approximately once per timebase cycle (~ 65 mc), interrupt flags CC3 and CC4 are setting, for which CC events and interrupt request generation are disabled during initialisation and never enable in main loop.It seems that the timebase Update event re-enables CC events and CC interrupt reqiests, but such behavior does not correspond to datasheet.Below is a picture from the analyzer and the text of the interrupt handler.

- Labels:

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-16 02:44 PM

Now I'm stuck with the fact that approximately once per timebase cycle (~ 65 mc), interrupt flags CC3 and CC4 are setting,

That's expected - they are set when CCRx == CNT, which, if you don't change CCRx to beyond ARR, occurs once every timebase cycle.

They don't trigger an interrupt though, if they are not enabled by the corresponding bits in DIER.

You simply should not check them in the ISR.

JW

- GLCD only half screen is working in STM32CubeIDE (MCUs)

- Understanding Output Data from I3G4250D Gyro Sensor on STM32F411e-Discovery in STM32 MCUs Embedded software

- Trigger from Timer does not trigger injected conversion on ADC in STM32 MCUs products

- STM32WLE5x NVIC RTC on Rev. Y die crash in STM32 MCUs Wireless

- ST-Link-V3 on MacBook Pro M2 running Sonoma 14.4 only works through hub in STM32 MCUs Boards and hardware tools