- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Timer DMA requests through DMA1 clarification

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Timer DMA requests through DMA1 clarification

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-24 01:32 AM

Hey everyone,

I need some clarification on this, as it will help my program run smoother.

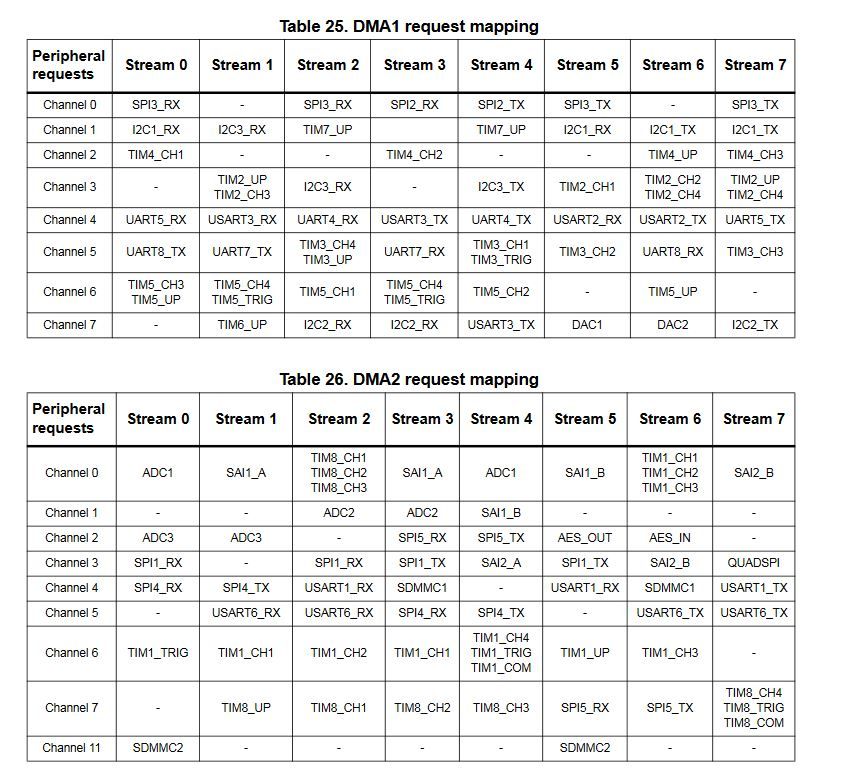

I want to run 2 DMA's simultaneously. One which will send data out using the SDMMC1, which is linked to DMA2. Then I'd like to read in data using DMA1 connected to Either of the Timer peripherals that allow a DMA request from GPIO to memory. Which here would be for example Timer 2 of DMA 1 stream 1.

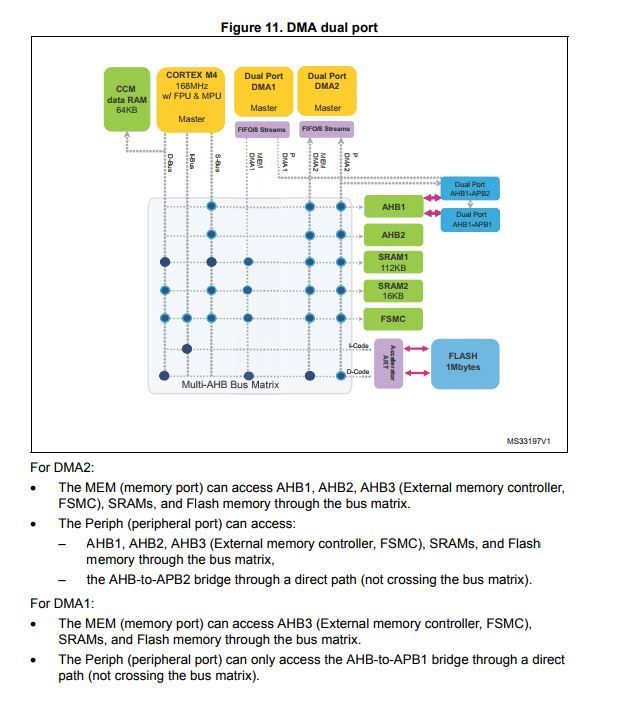

It doesn't seem like I can read in data from the GPIO to memory using DMA1 as seen in the image below from application note an 4 I've read on some forums that this could be because there is no direct connection between the DMA1 P and the bus matrix. So It would require me to go through a direct path. Is this possible as I haven't been able to get this going?

I'd like to have the two DMA's running independently to avoid a clash.

Thanks in advance for any help.

dma-gpio stm32f7-dma stm32f7Solved! Go to Solution.

- Labels:

-

DMA

-

STM32F7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-26 05:09 AM

what the direct path is that they refer to in an4031

That's when you access a peripheral through the dual-AHB/APB bridge (ie. when on the peripheral side of DMA, you use an address within its 'respective' APB address range).

This is the only option in DMA1. In DMA2, the other case - when you access APB through the bus matrix - happens if you access one of the APB1 peripherals from DMA2.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-24 12:30 PM

You can't use DMA1 for GPIO-to-memory access, fullstop.

You can have as many streams enabled simultaneously on DMA2 as much you want. They don't work simultaneously, but they follow the priorities assigned and natural, when several are triggered simultaneously.

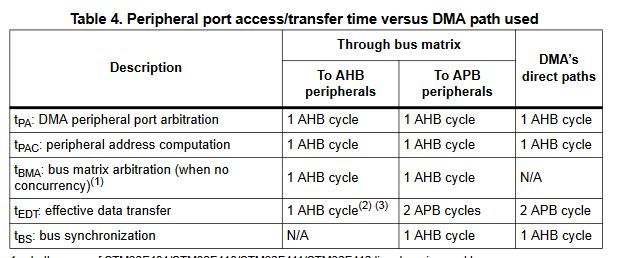

You always will have some 'clash' on the buses between several busmasters, if this is your concern. It's highly nontrivial to estimate its impact on any of the processes going on.

Read AN4031.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-24 12:43 PM

The Figure 11 seems to describe an F4 part, but your post more generally is about the F7

Some contention will occur due to the cycles involved, the system should manage most of these situations (check errata)

Both DMA1 and DMA2 have 8 independent internal units, so the system should be able to juggle 16 concurrent DMA operations.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-24 02:03 PM

The 'F7 have very same arrangement of the two DMA units as the 'F4, AFAIK. There may be details such as one, two or three RAM slave lines in the matrix, and DMA1 can connect to just several or all of them on its memory port, but IMO that's immaterial for this discussion.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-24 02:35 PM

My issue here is two fold, 1) mixed documentation is being reviewed, best to stick to the one for the platform being used lest wires get crossed or more confusion created, 2) ST has an F4 diagram in F7 documentation.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-24 03:29 PM

I see your point, Clive, however...

That Fig11 is from AN4031 (I did not realize Piet has already read it, sorry) and that appnote pertains to all 'F2, 'F4 and 'F7 (it says so in the title of AN, and also in the very chapter that Fig. is from). It serves as an illustration. Yes, it might've been made more 'generic' quite easily - yet highlighting the point, that DMA1 has access to a selection of memories on its memory port, i.e. no access to the peripheral AHBs there (thus no access to GPIO which on 'F2/'F4/'F7 sit on one of the AHBs); and no access to the bus matrix at all on the peripheral port - whereas DMA2 has it all.

This is just another 'proof' that the DMA arrangement is the same, although I admit there are DMA-related issues specific to 'F7 (user has to realize DMA-initiated operations are invisible to the cache; the DTCM is accessed through the APBS 'bridge', maybe there are more - I don't use F7 actively.)

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-26 04:39 AM

Hi Clive,

Thank you for the response. I just want to check something.

If I have Dma2 stream 8 and Dma2 stream 6 both trying to do a operation, lets say:

Dma2 stream 6: peripheral to memory

Dma2 stream 8: memory to peripheral

My understanding is that this can't happen simultaneously. One will occur and then the other?

I just want to check because of the statement you made:

Clive One wrote:

The Figure 11 seems to describe an F4 part, but your post more generally is about the F7

Some contention will occur due to the cycles involved, the system should manage most of these situations (check errata)

Both DMA1 and DMA2 have 8 independent internal units, so the system should be able to juggle 16 concurrent DMA operations.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-26 04:55 AM

Hi JW,

Firstly thank you for the reply.

I completely agree , although would you mind explaining what the direct path is that they refer to in an4031? I can see it throughout the application note.

I'll try to calculate the clash on the bus using an4

Thank you for all the help

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-26 05:05 AM

My understanding is that this can't happen simultaneously. One will occur and then the other?

The processes are more complex than this.

First, the memory-to-peripheral is influenced by pre-reading into FIFO.

Second, the arbitration happens at the memory and peripheral port separately.

Third, there may be processor or any other matrix-master accesses during the process, potentially fighting for slots on the target buses.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-26 05:09 AM

what the direct path is that they refer to in an4031

That's when you access a peripheral through the dual-AHB/APB bridge (ie. when on the peripheral side of DMA, you use an address within its 'respective' APB address range).

This is the only option in DMA1. In DMA2, the other case - when you access APB through the bus matrix - happens if you access one of the APB1 peripherals from DMA2.

JW

- U5 Website claim: 16.3 μA/MHz Run mode @ 3.3 V in STM32 MCUs products

- STM32H7B3 synchronous usart slave with a continuous clock in STM32 MCUs Embedded software

- How to abort SPI Slave when Master requests for less bytes? in STM32 MCUs products

- STM32H745 EXTI and SYSCFG_EXTICRx relation in STM32 MCUs Boards and hardware tools

- External Powering of NUCLEO-L031K6 HSI able to run? in STM32 MCUs Boards and hardware tools