- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Configuring DMA for SAI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Configuring DMA for SAI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-23 08:40 AM

Hi,

I'm trying to transfer data to SAI's fifo via DMA (memory-to-peripheral). I'm following reference manual's instructions for setting up DMA for SAI.

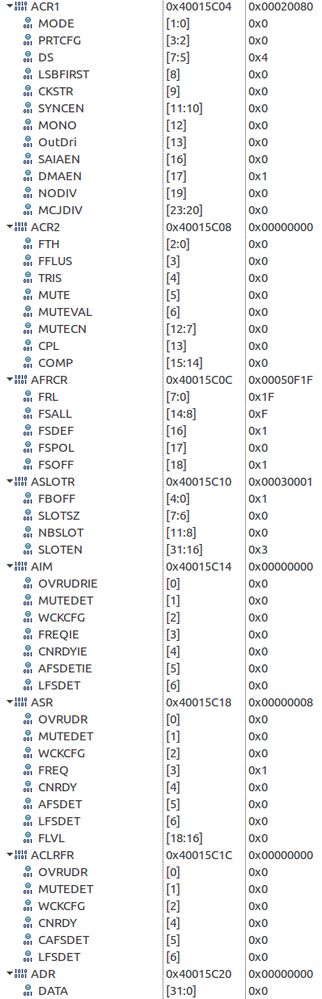

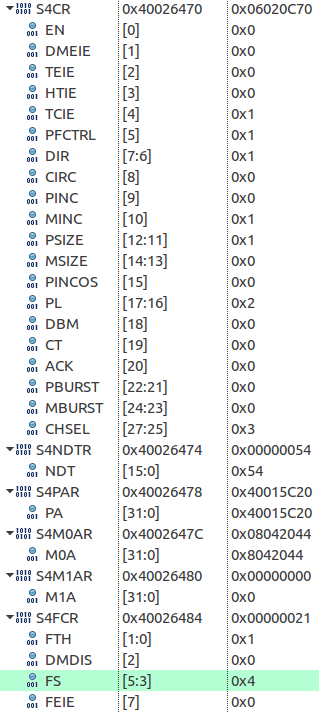

As soon as I enable the DMA channel FEIF4 (FIFO overrun/underrun) flag becomes active. After enabling the SAI2 interface and waiting few clock cycles TEIF4 (Transfer error) flag becomes active and disables the DMA channel. I've attached SAI2 A and DMA2 stream 4 register values below. I have no experience with DMA or SAI so maybe there's something wrong with the registers. If the registers seem OK could this be clock issue? Any help would be greatly appreciated. Please ask more info if you need to.

MCU: STM32F446ZE

SAI2 A REGISTERS

DMA2 STREAM 4 REGISTERS

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-23 09:21 AM

Don't set PFCTRL in DMAStream_CR - read 9.3.16 Flow controller.

In direct mode, you should ignore the FEIF - there's an explanation somewhere in the forum why this happens but now the forum is in havoc and I'm not going to look it up.

You may want to set the FIFO threshold somewhat higher than empty, otherwise the FIFO is effectively unused.

Your SLOTR appears to be inconsistent: you set (by SLOTSZ =0) slot size equal to data size, yet try to shift the slot by FBOFF (it's ineffective but should be 0 nonetheless - the characteristic I2S 1-bit shift is already accomplished by setting FRCR.FSOFF=1); you set only one slot per frame in NBSLOT yet enable two in the SLOTEN bitmask. This btw violates the requirement for 'The number of slots should be even if FSDEF bit in the SAI_xFRCR register is set.'

JW

PS. What debugger is this? SAI_CR1.MCKDIV is misspelled as MCJDIV... 🙂

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-23 09:21 AM

Don't set PFCTRL in DMAStream_CR - read 9.3.16 Flow controller.

In direct mode, you should ignore the FEIF - there's an explanation somewhere in the forum why this happens but now the forum is in havoc and I'm not going to look it up.

You may want to set the FIFO threshold somewhat higher than empty, otherwise the FIFO is effectively unused.

Your SLOTR appears to be inconsistent: you set (by SLOTSZ =0) slot size equal to data size, yet try to shift the slot by FBOFF (it's ineffective but should be 0 nonetheless - the characteristic I2S 1-bit shift is already accomplished by setting FRCR.FSOFF=1); you set only one slot per frame in NBSLOT yet enable two in the SLOTEN bitmask. This btw violates the requirement for 'The number of slots should be even if FSDEF bit in the SAI_xFRCR register is set.'

JW

PS. What debugger is this? SAI_CR1.MCKDIV is misspelled as MCJDIV... 🙂

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-24 04:41 AM

Thanks! I got DMA working with your instructions. Now I have to study how slots work.

waclawek.jan wrote:

PS. What debugger is this? SAI_CR1.MCKDIV is misspelled as MCJDIV... 🙂

The register viewer is a GNU ARM Eclipse plug-in.

- CRC32 MPEG2 configuration for ST32C0x1 CRC driver in STM32 MCUs products

- STM32CubeMX different configurations for the same project in STM32 MCUs TouchGFX and GUI

- SPI NSS/CS when working with registers and DMA in STM32 MCUs products

- Configuring ITM on STM32U5 in STM32 MCUs Embedded software

- STM32H745BI SPI port does not start in STM32 MCUs products