- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Why do spi transfer insert delays between byte tra...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Why do spi transfer insert delays between byte transfers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-05 06:53 AM

STM32F091xc processor

One spi controller

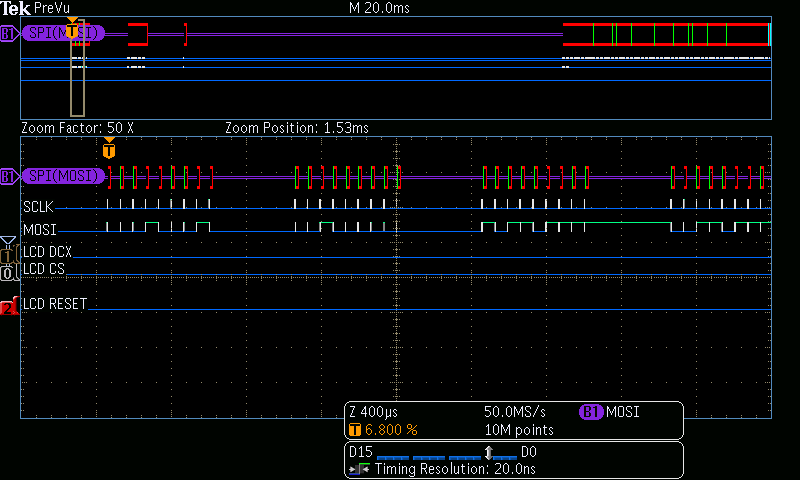

I'm doing transfers to a LCD. The LCD appears to somewhat work. However the colors and orientation seems odd. I looked at the SPI bus on Logic Analyzer and I get delays between every 9 bytes. I'm thinking these delays between packet bursts are the culprit. ie. a cmd just happens to be on a 9th byte and then the micro inserts a large delay between the cmd arguments and the cmd is ignored by the LCD.

For instance here is the screenshot of the byte transfers. I looked at the errata for this processor but I did not see anything related to SPI in master mode. I'm using the HAL_SPI_Transmit() routine. Note, one potential problem is that I am doing the transfers one byte at a time. However these delays were not present in 32f072 cpu based board.

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-05 08:27 AM

Fixed this issue. Here was the problem and the solution. I used the cube tool to generate the project. Using the defaults, the System Clock Mux was using the HSI clock source instead of the HSI48. This meant the APB1 peripheral clock was maxed out at 8Mhz instead of 48Mhz. Changing the mux to use the HSI48 fixed the delays between long byte transfers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-05 08:27 AM

Fixed this issue. Here was the problem and the solution. I used the cube tool to generate the project. Using the defaults, the System Clock Mux was using the HSI clock source instead of the HSI48. This meant the APB1 peripheral clock was maxed out at 8Mhz instead of 48Mhz. Changing the mux to use the HSI48 fixed the delays between long byte transfers.