- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- How do I Atomic Operation control the non-bit band...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How do I Atomic Operation control the non-bit banding region in STM32F4 and STM32F1 ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-01 12:54 AM

Hi,

Currently I'm studying for bit-banding.

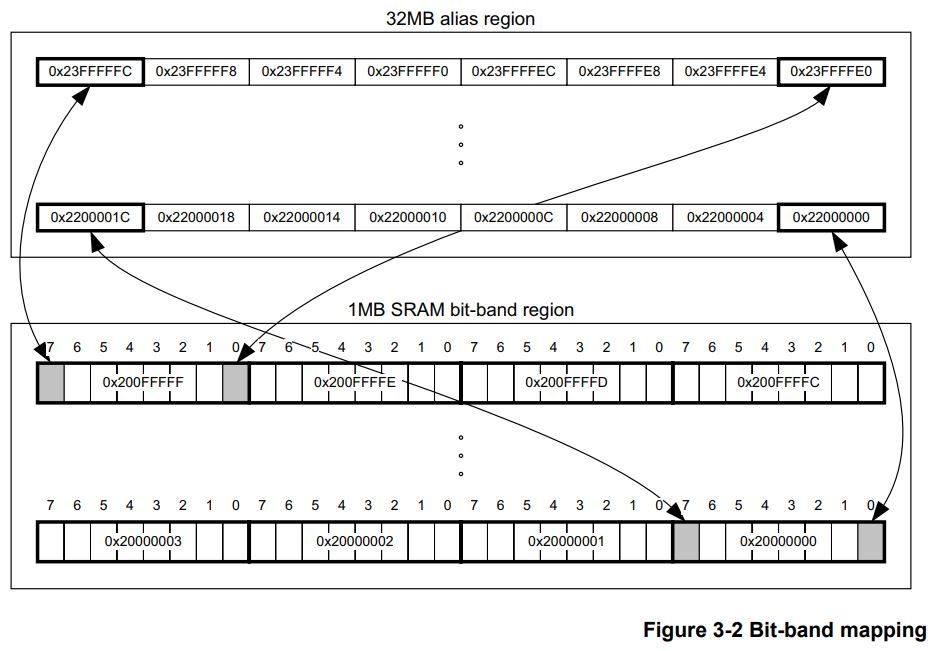

As I understad, the bit bit-banding works as Bit-banding maps a complete word of memory onto a single bit in the bit-band region fromhttp://infocenter.arm.com/help/topic/com.arm.doc.ddi0337h/DDI0337H_cortex_m3_r2p0_trm.pdf

Q1.

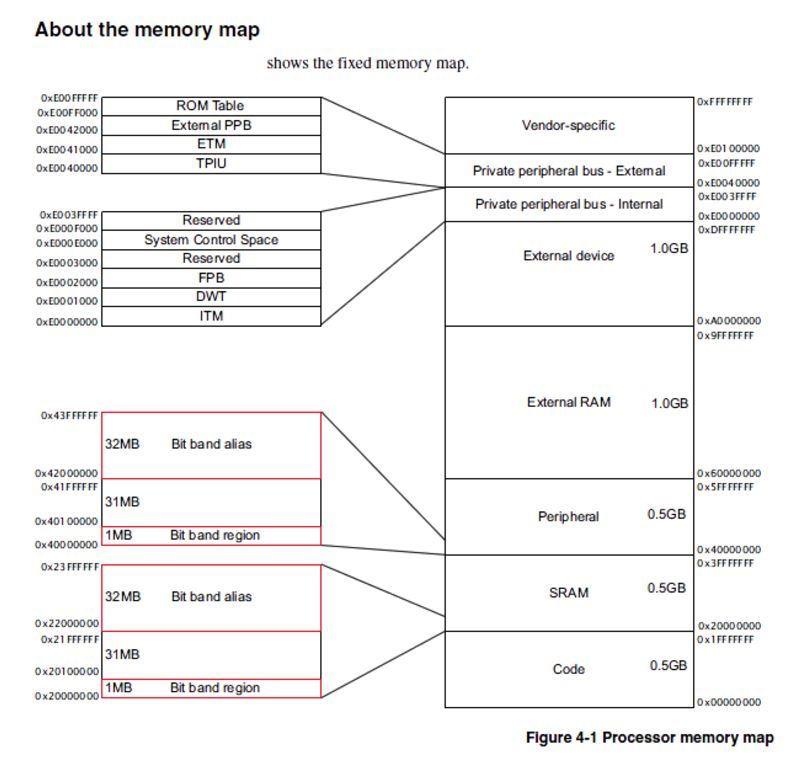

But I'm wondering how do I Atomic Operation control non-Bit Band Alias region in memory map.For example, in the below M3 memory map.We can see 2 Bit band alias part(red box), it means that Bit band region can be aliaed.But how do I control non-Bit band Alias part in memory map such as External Device, External RAM and Private peripheral bus region?So I want to know what common method exist in non-bit band region.

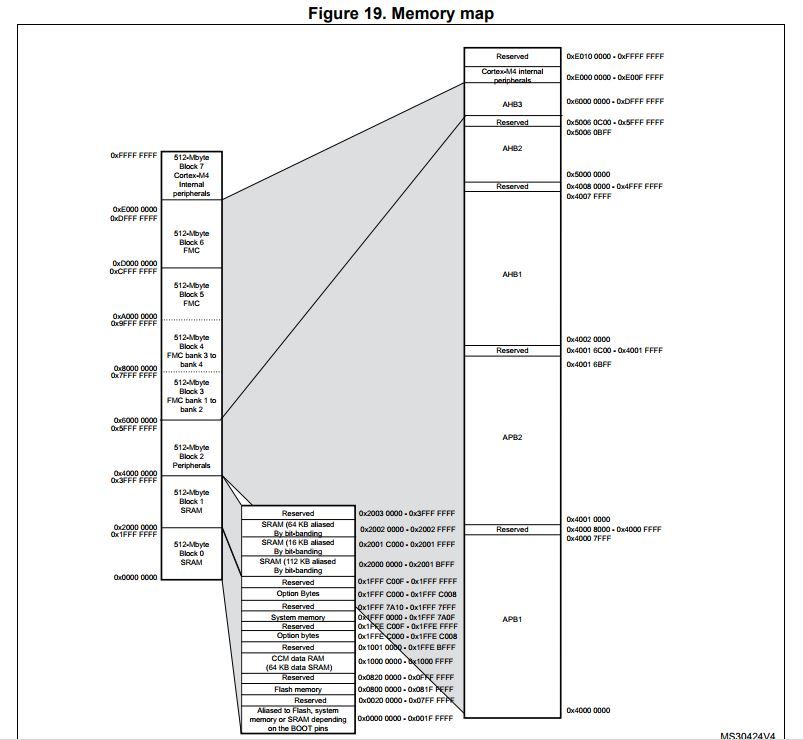

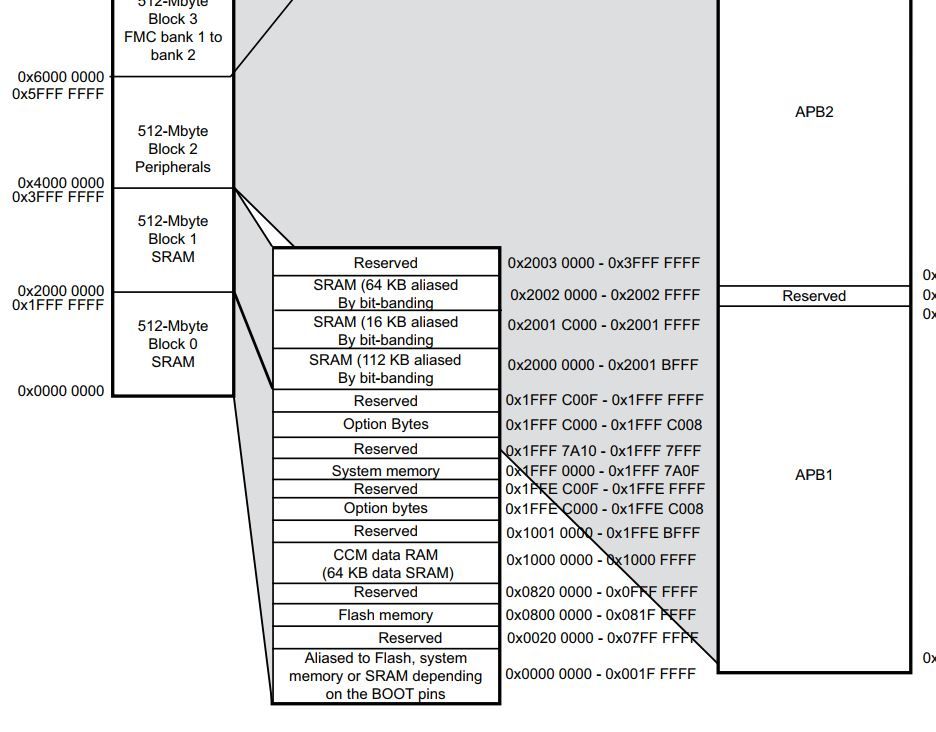

Q2.The following is STM32F429xx M4 memory map.

We can see 3 Alias region (64KB,16KB,112KB aliased By bit-banding). but where exactly 3 alias regions indicate alias?In case M3(in Q1), each bit band alias has paired to Bit band region. but I can't find that pair region in STM32F429xx M4 memory map.How can I understand this?and Here's also very small size align region. I think STM32F429xx has to have more than M3. but there are just 3 region. I can't understand it. How can I Atomic Operation in non bit banding alias region? I want to know most common way.

#bit-banding-stm32f4 #bit-banding #bit-banding-stm32f1

#bit-banding-stm32f4 #bit-banding #bit-banding-stm32f1

- Labels:

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-01 01:17 AM

But I'm wondering how do I control non-BitBand Alias part in memory map.

You don't control anything of bit-banding, this is a built in and fixed option.

Bit-banding works in the following way: on the output of processor (its S-port to be precise), where it attaches to the bus matrix, there is a small insert with an address comparator for the 22000000-23ffffff and 42000000-43ffffff addresses.

Whenever the processor tries to read from one of those areas, this insert intercepts the read, transforms the address to the non-bit-band version, performs the read but retains the result, extracts the given bit according to the original address to produce 0x00000000 or 0x00000001 and submits it to the processor.

Whenever the processor tries to write to one of those areas, this insert intercepts the write, transforms the address to the non-bit-band version, performs a read from that address while locking down the target bus (i.e. no other master (such as DMA) can access the bus), in the read data replaces the bit given by original address by the lowest bit from data written by processor, and writes back the result to the non-bit-band version of address, while unlocking the bus.

Note, that this is present only in Cortex-M3 and M4, *not* in M0/M0+ and *not even* in M7, so if you intend to migrate upwards or downwards, better don't use it. Note also, that this insert is a configuration option, and while all STM32 M3/M4 contain it, some other vendors chose not to use it (e.g. some of the ATSAMs), so if you intend to migrate across mcu vendors, better don't use it.

[shameless self-advertisement]

http://www.efton.sk/STM32/bitbandcalc.html

[/shameless self-advertisement]JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-01 02:10 AM

If you need to do atomic operations (not necessarily limited to bit-band ones) on non-bit-band memory, you are forced to use 'other means' to achieve the atomicity.

For example you could disable all interrupts*, do the operation and then restore interrupts. That's what I had to do when porting bit-band code to stm32f7. The details will vary depending on your environment (e.g. if you're using a real-time operating-system, and if so which). This code uses Rowley's Crossworks Tasking Library:

/* stm32f7 does not have bit-banding */

#define DISABLE_INTERRUPTS int en = ctl_global_interrupts_disable()

#define ENABLE_INTERRUPTS if (en) ctl_global_interrupts_enable()

void peripheral_bitband_write(volatile unsigned *address, int bit, unsigned int value)

{

DISABLE_INTERRUPTS;

*address = (*address & ~(1 << bit)) | (value ? 1 << bit : 0);

ENABLE_INTERRUPTS;

}

*This isn't sufficient if DMA activity could modify the memory word.

Hope this helps,

Danish

- Facing issue in transfering SDcard file by UART, USB functionality is not achieved by using 2 STM32 in STM32 MCUs Embedded software

- DMA RX complete interrupt sometimes not called in STM32L4 in STM32 MCUs products

- Malloc Calloc operations in STM32F4 without RTOS in STM32 MCUs products

- Switching QSPI flash to indirect mode w/o suspending TouchGFX thread? in STM32 MCUs TouchGFX and GUI

- how to get the list of bug for STM32F4 Series, STM32F1 Series in STM32 MCUs products