- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- is it available to get 9MHZ PWM from STM32F334

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

is it available to get 9MHZ PWM from STM32F334

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-21 01:58 AM

Hi ST,

my purpose is to use STM32F334 to output 9MHZ PWM ,and need to adjust the pulse width each period by the burst DMA of the chip, is it available ? thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-22 05:48 AM

AN4776 Chapter 5

If you don't want to adjust both period and duty cycle, but only duty cycle, you don't need a DMA 'burst', just a plain DMA write to given TIMx_CCRy register.

9MHz sounds a bit high frequency though, did you intend to use the HRTIM?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-22 06:07 AM

This is ST's forum, but most of the support comes from users here.

Seems rather high to need modulating on a cycle-by-cycle basis, have you considered a CPLD?

DMA would just write a new CCRx value on each Update, but I think 9 MHz would cause some considerable contention, and your buffer would need to be rather large to stop the interrupt loading from saturating the processor.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-22 06:13 AM

Hi JW, thank you for your reply.

Yes , use the HRTIM, the purpose is to output SPWM at 9MHZ carrier wave , just want to confirm if STM32F334 is fast enough to adjust the duty cycle at each period(9MHZ) by DMA. I checked the table 83 at Referece manual 'RM0364',0-100% duty cycle is impossible , but it is also OK to get 20%-80% for my application;

It would be apprecated if there is SPWM sample with HRTIM

Thanks,

JL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-22 07:46 AM

Hi Clive,

thank you for your reply,

use HRTIM with DAM to update the duty cycle instead of interrupt method. The duty resulotion is up to 217ps.

But , how many clock cycles to update the set of the registers by each DMA transfer,I can't get the clear informtion from ST datasheet , from

the table 83 of Referece manual 'RM0364' , I guess it is 3 cycles at 72MHZ .

I have to wait ST guy's answer.

Thanks,

J L

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-22 08:47 AM

I think 9 MHz should be doable, but at 72 MHz that would be 8 cycles, so adjustment of duty is going to be rather coarse.

0 is OFF (0%), 8 is ON (100%), 1 is 12.5%

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-22 10:19 AM

It depends on how the output is being used. DAC for precise analog output if possible.

Then if 9 MHz, you would have 10 steps at 90MHz and 20 steps at 180MHz raw.

Of course, you can use DMA looping through 2,4,8,16 duty cycles to implement dithering if allowed.

==> Dithering example: If 10 steps, by changing every timer period the duty cycle between both 30 and 40% value, you get averaged 35% with half timer period modulation.

With a more detailed knowledge of the HW, the architecture choice can be refined.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-22 03:33 PM

how many clock cycles to update the set of the registers by each DMA transfer,I can't get the clear informtion from ST datasheet , from

the table 83 of Referece manual ''RM0364'' , I guess it is 3 cycles at 72MHZ

More like 6 AHB + 2 APB cycles, if there's no collision with other masters on the buses and no other DMA channel active - this might be a showstopper.

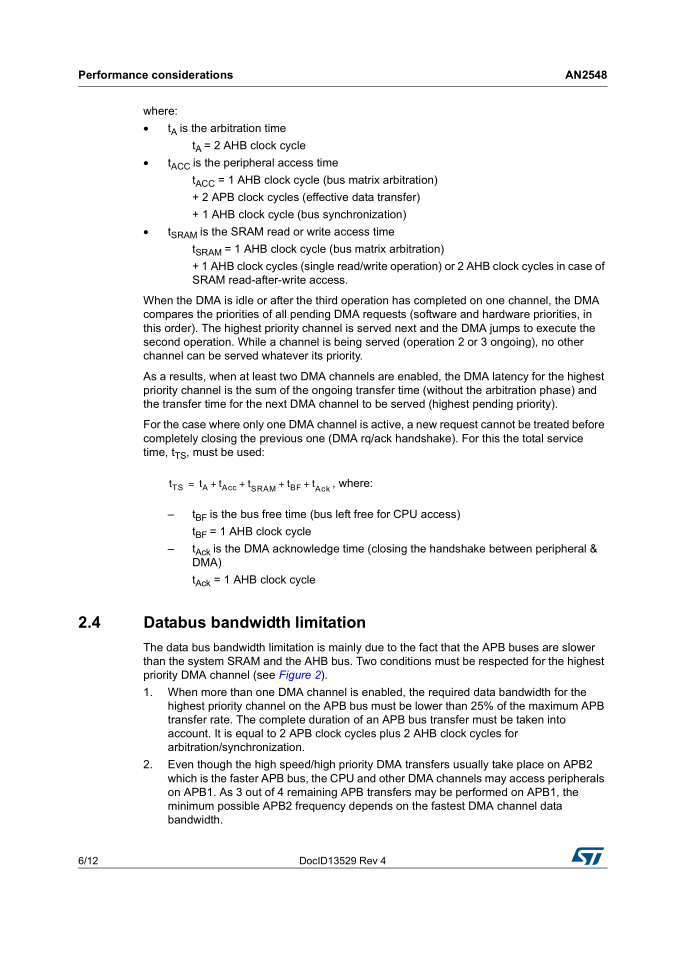

I know AN2548 is for 'F1 and 'L1, but the DMA in 'F3 appears to be of the same design.

I'd recommend you to write a simple test application, perhaps on a Disco or Nucleo, before commencing with design. Using external modulator as Clive suggested above is always a sure bet of course.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-22 08:52 PM

Thanks JW,

How many latency cycles at HRTIM DMA on STM32F334 , hope to get the ST official answer soon ...