- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Regarding ADC error

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Regarding ADC error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-27 12:22 AM

Dear all.

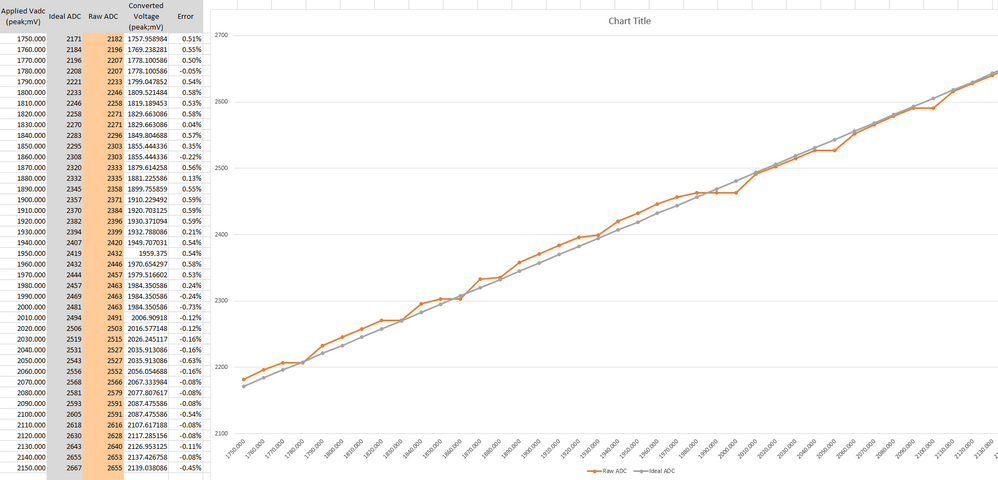

I measured ACD input increasing the voltage by 10mVdc. but, there are non-nonlinear points.

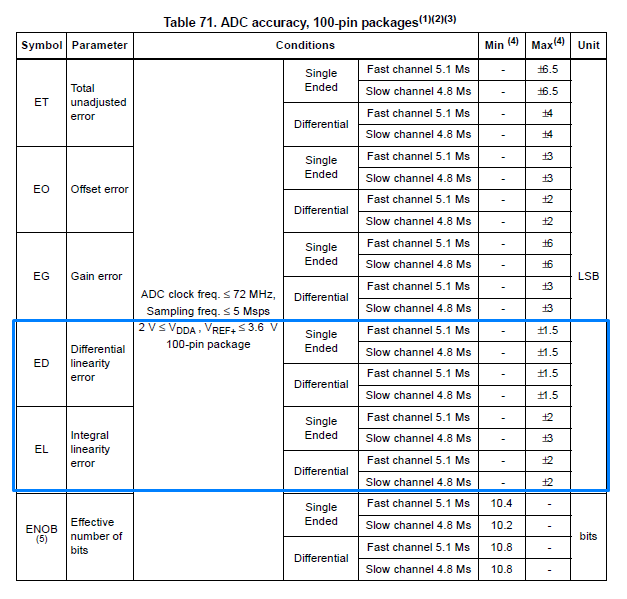

As the datasheet, ED and EL are +-1.5LSB and +_2LSB. It seems that my measurement result is bigger than them.

Could you please explain how to reduce the error?

Thank you in advance.

Vref : 3.3V

ADC clock : 72Mhz / 2 = 36Mhz

1 LSB : 3.3V / 4096 = 0.805664063

ADC channel : Fast channel ADC1 3channel

Sampling mode : Single-ended

Sampling time : ADC_SampleTime_7Cycles5

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-27 01:34 AM

Have you checked that your test conditions (electrical and software settings like sample time) match those stated in the datasheet you cited ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-27 05:26 PM

I think below my condition was satisfied with those test condition on the table.

- ADC clock freq : 36Mhz <= 72Mhz

- Sampling freq : 2.57Msps <= 5Msps

- ADC clock = 36Mhz

- Tconv = 7.5+12.5 = 20 ADC clock cycles

- Sampling freq. = 20 / 36*10^6 = 555.55ns; 1.8Msps

- Vdda = Vref+ = 3.3V

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-28 12:16 AM

The PCB design / layout has a significant influence, as have the tolerence and impedance of your (reference) input voltage source.

If you think some STM32 MCUs have a problem with the ADC peripheral, better discuss it with a ST FAE.

Most people here, like me, are users, and need to rely on the same documentation as you.

And the ST people present here are rarely hardware experts.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-28 04:39 AM

Thank you for your comment. I'll discover the possible causes you mentioned.

- Download Error "This software is not available for download." in STM32CubeIDE (MCUs)

- STM32CubeIDE crashes - Problem: EXC_BAD_ACCESS (SIGABRT) in STM32CubeIDE (MCUs)

- Error in Nucleo-U031R8 SCK Connection in STM32 MCUs Boards and hardware tools

- undefined reference to `videoTaskFunc(void*)' in a project with cpp target language in STM32 MCUs TouchGFX and GUI

- Two boards STM32H757I-EVAL seem dead after USART1 (CN2) to RS232 connection in STM32 MCUs Boards and hardware tools