- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- State of GPIOs for STM32H7 MCUs

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

State of GPIOs for STM32H7 MCUs

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-05 10:35 PM

Hi can someone please point me to the relevant datasheet that describes the state of the STM32H7 GPIO pins during the following conditions:

1) During power up

2) Just after reset (when the Power On Reset is released)

My understanding is this:

1)

During power up -

High Impedance2) After

Power On Reset is released -

Analog InputIn application mode, of course the state of the GPIO will be set according to user configuration.

Cant seem to find this information in the STM32H7 data sheets

Many thanks.

- Labels:

-

GPIO-EXTI

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-06 12:25 AM

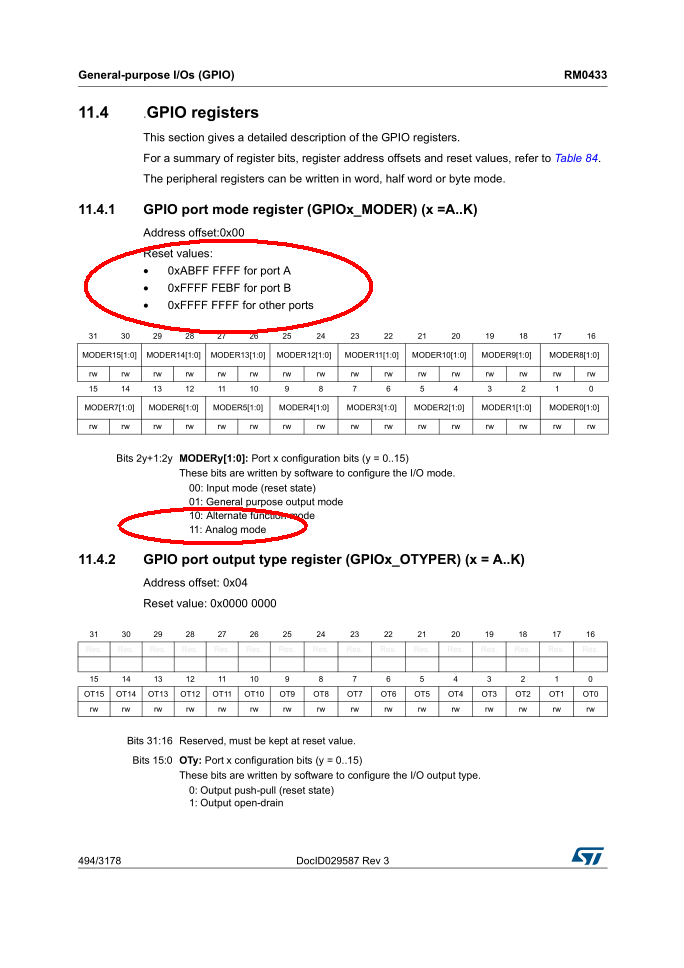

I don't see a reason why would GPIOs have different mode during and after reset (assuming power-on reset, and except when entering bootloader or exiting from some of the low power modes). However, there *is* a discrepancy in the RM: while the narrative in 11.3.1 General-purpose I/O (GPIO) says:

During and just after reset, the alternate functions are not active and most of the I/O ports

are configured in input floating mode.whereas - contrary to 'F7 - the GPIO chapter indicates that most of the pins go to Analog mode in reset:

I know it's unlikely to happen, but I'd 1ove to heare ST's take on this.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-06 07:46 PM

Thanks for the feedback JW.

From reading through the data sheets and in particular Section 11 from the RM0433 Reference Manual for the STM32H7 I have determined the following:

During and just after reset the GPIO's are in the following state:

Pins PA15, PA14, PA13,

PB4 and PB3

on Ports A and B are set toJTAG-DP (Debug Port)

PA15 = JTDI (Input, internal pull-up enabled)

PA14 = JTCK-SWCLK (Input, internal pull-down enabled)

PA13 = JTMS-SWDIO (Input, internal pull-up enabled)

PB4 = NJTRST (Input,

internal pull-up enabled

)PB3 = JTDO/TRACESWO (Output, n

o pull-up, pull-down

)The contents of the control registers are set to

the following configuration:

GPIO_MODER = Alternate function mode

GPIO_OTYPER = Output push-pull

GPIO_OSPEEDR = PA15, PA14 and PB4 = Low speed, PA13 and PB3 = Very high speed

GPIO_PUPDR = PA15, PA13 and PB4 = Pull-up, PA14 = Pull-down, PB3 =

No pull-up, pull-down

GPIO_IDR = Not Applicable

GPIO_ODR = Not Applicable

GPIO_BSRR = Not Applicable

GPIO_LCKR = Port configuration not locked

GPIO_AFRL = Alternate Function 0 selected

GPIO_AFRH =

Alternate Function 0 selected

The remaining pins on Ports A to K are set to

Analog m

ode

defined by the following configuration:GPIO_MODER = Analog mode

GPIO_OTYPER = Output push-pull

GPIO_OSPEEDR = Low speed

GPIO_PUPDR = No pull-up, pull-down

GPIO_IDR = Not Applicable

GPIO_ODR = Not Applicable

GPIO_BSRR = Not Applicable

GPIO_LCKR = Port configuration not locked

GPIO_AFRL = Alternate Function 0 selected

GPIO_AFRH =

Alternate Function 0 selected (note Port K 8..15 not supported)

Pin NameFunction (after reset)I/O State (after reset)

PA15JTDIInput, internal pull-up enabled

PA14JTCK-SWCLKInput, internal pull-down enabled

PA13JTMS-SWDIOInput, internal pull-up enabled

PB4NJTRSTInput, internal pull-up enabled

PB3JTDO/TRACESWOOutput, no pull-up, pull-down

All othersAnalog modeInput, no pull-up, pull-down

- STM32F401 - using OSC_IN/OSC_OUT as GPIO in STM32 MCUs products

- stm32h7 fastest gpio read using DMA in STM32 MCUs products

- High current consumption in Stop Mode on STM32U575 DEV Kit and Custom Board in STM32 MCUs products

- Subject: STM32H753ZI cannot control PC02 as GPIO or SPI2_MISO functionality. in STM32 MCUs products

- AN6091 ('L0->'U0 migration) comments in STM32 MCUs products