- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Minimum HCLK frequency for STM32L433CC in CubeMX

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Minimum HCLK frequency for STM32L433CC in CubeMX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-21 02:33 AM

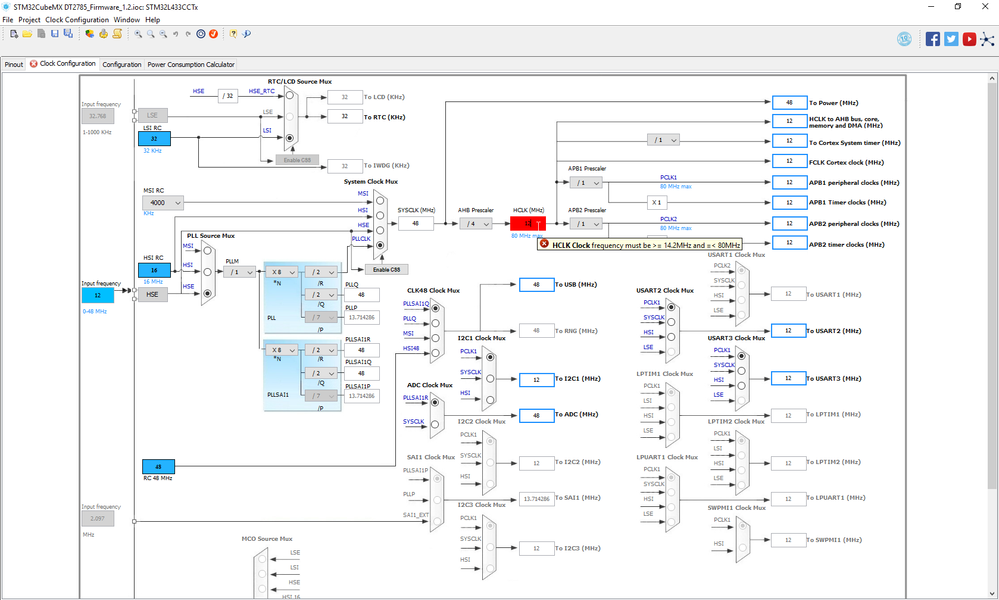

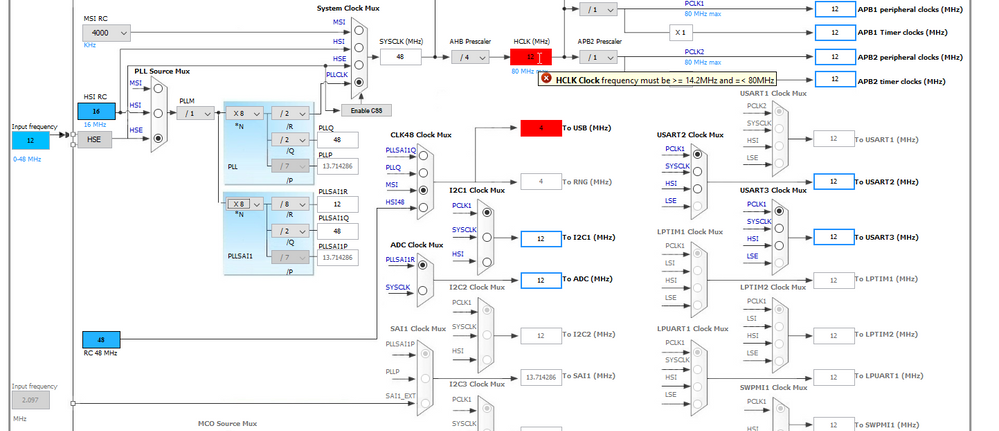

CubeMX doesn't like a frequency of 12 MHz for HCLK with the STM32L433CC.

HCLK is suggested to be at least 14.2 MHz, but I couldn't find any such requirement in the reference manual or datasheet.

The F4 RM0090 mentions: ''To guarantee a correct operation for the USB OTG FS peripheral, the AHB frequency should be higher than 14.2 MHz.''

Does this apply to the L4 series as well?

Kind Regards,

Moritz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-21 04:25 AM

You have peripherals clocking at 48 MHz.

Select 4 MHz MSI for ADC and CLK48-USB

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-21 08:06 AM

Sorry, I don't understand your answer. MSI can't be selected for ADC, USB isn't happy with anything else than 48 MHz and HCLK still requests more than 12 MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-21 08:14 AM

But you could use SYSCLK, why is SYSCLK at 48 MHz if you want to run the part at 12 MHz?

There is likely something CubeMX doesn't like, or as usual it is broken in some way, the part can definitely run at 12 MHz, but it seems to be warning about a potential clock inversion issue.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-21 08:32 AM

Yes, you are right. It would be more sensible to drive SYSCLK directly from HSE.

I am not sure the part really can run at 12 MHz while using USB. The file 'stm32l4xx_hal_pcd.c' assumes a HCLK of at least 14.2 MHz:

void HAL_PCD_IRQHandler(PCD_HandleTypeDef *hpcd)

{...

hclk = HAL_RCC_GetHCLKFreq();

if ((hclk >= 14200000U) && (hclk < 15000000U))

{ /* hclk Clock Range between 14.2-15 MHz */ hpcd->Instance->GUSBCFG |= (uint32_t)((0xFU << 10) & USB_OTG_GUSBCFG_TRDT); }else if ((hclk >= 15000000U) && (hclk < 16000000U))

...

else /* if(hclk >= 32000000) */

{ /* hclk Clock Range between 32-200 MHz */ hpcd->Instance->GUSBCFG |= (uint32_t)((0x6U << 10) & USB_OTG_GUSBCFG_TRDT); }...

}

This function has no case for HCLK values below 14.2 MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-21 09:01 AM

On the other hand this code is not executed on the STM32L433CC, which doesn't have a register called GUSBCFG. I assume the 14.2 MHz constraint only applies to STM32L4 parts with USB OTG functionality.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-21 09:37 AM

I assume the 14.2 MHz constraint only applies to STM32L4 parts with USB OTG functionality.

Yes, you are right; it's valid only for the higher-end 'L4. This is probably a bug in CubeMX.

There is a constraint, though, although different (see RM0394):

Note: Due to USB data rate and packet memory interface requirements, the APB clock must have

a minimum frequency of 10 MHz to avoid data overrun/underrun problems.JW

- STM32U5xx: SPDIF out - how to configure? in STM32 MCUs products

- Input capture not detecting square wave in STM32 MCUs products

- Issue in Input capture for overflow condition. in STM32CubeIDE (MCUs)

- STM32H573 not reaching 250 MHz in STM32 MCUs products

- stm32wl communication data error with SX1278 in STM32 MCUs Wireless