Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- Knowledge base

- STM32 MCUs

- FAQ: Default State of STM32H7 switches connecting ...

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

FAQ: Default State of STM32H7 switches connecting Pxy_C and Pxy pads

Christophe VRIGNAUD

ST Employee

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

on 2021-01-05 07:52 AM

What is the state after reset of STM32H7 analog switches between Pxy_C and Pxy pins/balls?

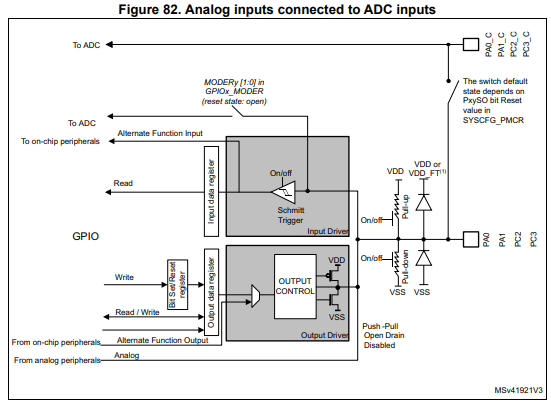

The Reference Manual RM0399 Rev 3 (page 584) gives a figure as the one below , but not all Pxy_C and Pxy are accessible depending on the STM32H7 package.

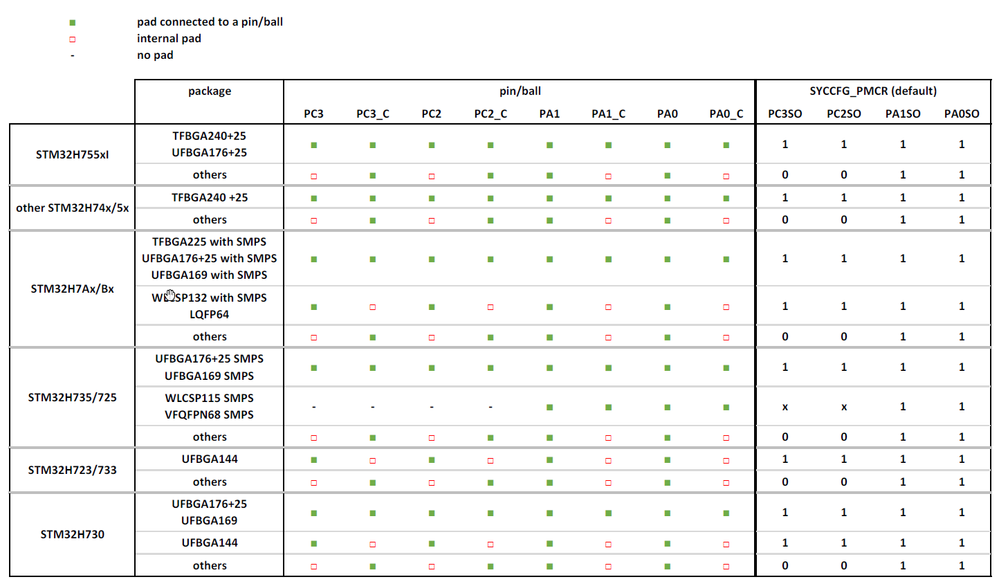

The default state of the analog switches can be deduced from the STM32H7 package and can be read with a debugger.1. Rules

- GPIOs are in analog mode during and just after reset (except the debug pins in alternate function mode after reset).

- But the digital alternate functions are accessible after reset whatever the package.

2. Default state

According to these rules, the default state of the switches depends on the package:- If both Pxy and Pxy_C are available, the corresponding switch that connects the two internal pads is open by default.

- The alternate functions are accessible through Pxy pin/ball while the ADC input is available through Pxy_C pin/ball.

- If only Pxy is available, the switch is open by default.

- The alternate functions are accessible through Pxy pin/ball. To use the ADC connected to the internal pad Pxy_C, the switch shall be closed. In this case, the other functions of the Pxy pin/ball are no more accessible.

- If only Pxy_C is available, the switch is closed by default.

- The alternate functions are accessible through Pxy_C pin/ball. To use the ADC connected to the internal pad Pxy_C, the switch shall be opened.

3. SYSCFG peripheral mode configuration register (SYSCFG_PMCR)

The switch state can be read/modified in SYSCFG_PMCR.PxySO (Pxy Switch Open):0: Analog switch closed (pads are connected through the analog switch)

1: Analog switch open (2 separated pads)

At this point, the datasheet is needed to know which pins are available on the STM32H7 package (pinout/ballout figure and pin/ball definition table).

The value of this SYSCFG_PMCR register can also be read in a debugger (after having enabled the clock by __HAL_RCC_SYSCFG_CLK_ENABLE()).

4. Examples

Labels: